Intel Sapphire Rapid-SP Xeon將配備高達64GB HBM2e,並討論2023年及以後的下一代Xeon和數據中心GPU

在 SC21(Supercomputing 2021)上,Intel舉辦了一個簡短的會議,討論了他們的下一代數據中心路線圖,並討論了他們即將推出的Ponte Vecchio GPU和Sapphire Rapids-SP Xeon CPU。

Intel已經在Hot Chips 33上討論了有關其下一代數據中心CPU和GPU產品的大部分技術細節。他們重申了他們所說的話,並在SuperComputing 21上透露了更多花絮。

據Intel稱Sapphire Rapids-SP將提供兩種封裝版本,一種標準配置和一種HBM配置。標準版本將採用由四個XCC晶片組成的小晶片設計,晶片尺寸約為400mm2。這是單個XCC晶片的晶片尺寸,頂級Sapphire Rapids-SP Xeon上總共有四個晶片。每個管芯將透過EMIB互連,EMIB的間距大小為55u,核心間距為100u。

標準的Sapphire Rapids-SP Xeon將擁有10個EMIB互連,整個封裝的尺寸為4446mm2。轉向HBM版本,獲得了更多的互連,它們擁有14個,需要將HBM2E互連到核心。四個HBM2E將採用8-Hi堆棧,因此Intel計劃每個堆棧至少配備16GB的HBM2E,在Sapphire Rapids-SP中總共有64GB。談到封裝,HBM版本的尺寸將達到驚人的5700mm2比標準版本大28%。與最近洩露的EPYC Genoa相比,Sapphire Rapids-SP的HBM2E封裝版本最終將大5%,而標準封裝將小22%。

- Intel Sapphire Rapids-SP Xeon (Standard Package) – 4446mm2

- Intel Sapphire Rapids-SP Xeon (HBM2E Package) – 5700mm2

- AMD EPYC Genoa (12 CCD Package) – 5428mm2

Intel還表示與標準封裝設計相比,EMIB提供兩倍的頻寬密度改進和4倍的電源效率。有趣的是Intel將最新的Xeon產品線稱為邏輯單片,這意味著它們指的是提供與單晶片相同功能的互連,但從技術上講有四個小晶片將互連在一起。

接著轉向Ponte Vecchio,Intel概述了其旗艦數據中心GPU的一些關鍵特性,例如128個Xe核心、128個RT單元、HBM2e以及總共8個將連接在一起的Xe-HPC GPU。該晶片將在兩個獨立的堆棧中提供高達408MB的L2快取,這些堆棧將透過EMIB互連進行連接。該晶片將採用Intel自己的“Intel 7”製程和台積電N7/N5 製程的多個晶片。

Intel此前還詳細介紹了其採用Xe-HPC架構的旗艦Ponte Vecchio GPU的封裝和晶片尺寸。該晶片將由2個tiles組成,每疊有16個活動晶片。最大活動頂部晶片尺寸將為41mm2,而基礎晶片尺寸(也稱為Compute Tile)為650mm2。Ponte Vecchio GPU使用8個HBM 8-Hi堆棧並包含總共11個EMIB互連。整個Ponte Vecchio封裝的尺寸為4843.75mm2。Intel還提到使用高密度3D Forveros封裝的Meteor Lake CPU的凸點間距將為36u。

除此之外Intel還發布了一份路線圖,其中確認下一代 Xeon Sapphire Rapids-SP系列和Ponte Vecchio GPU將於2022年上市,但還有計劃於2023年及以後推出的下一代產品.,Intel尚未明確說明其計劃帶來什麼,但我們知道Sapphire Rapids的繼任者將被稱為Emerald和Granite Rapids,而其繼任者將被稱為Diamond Rapids。

對於GPU方面,我們不知道Ponte Vecchio的繼任者會是什麼,但預計它將與NVIDIA和AMD的下一代GPU競爭數據中心市場。

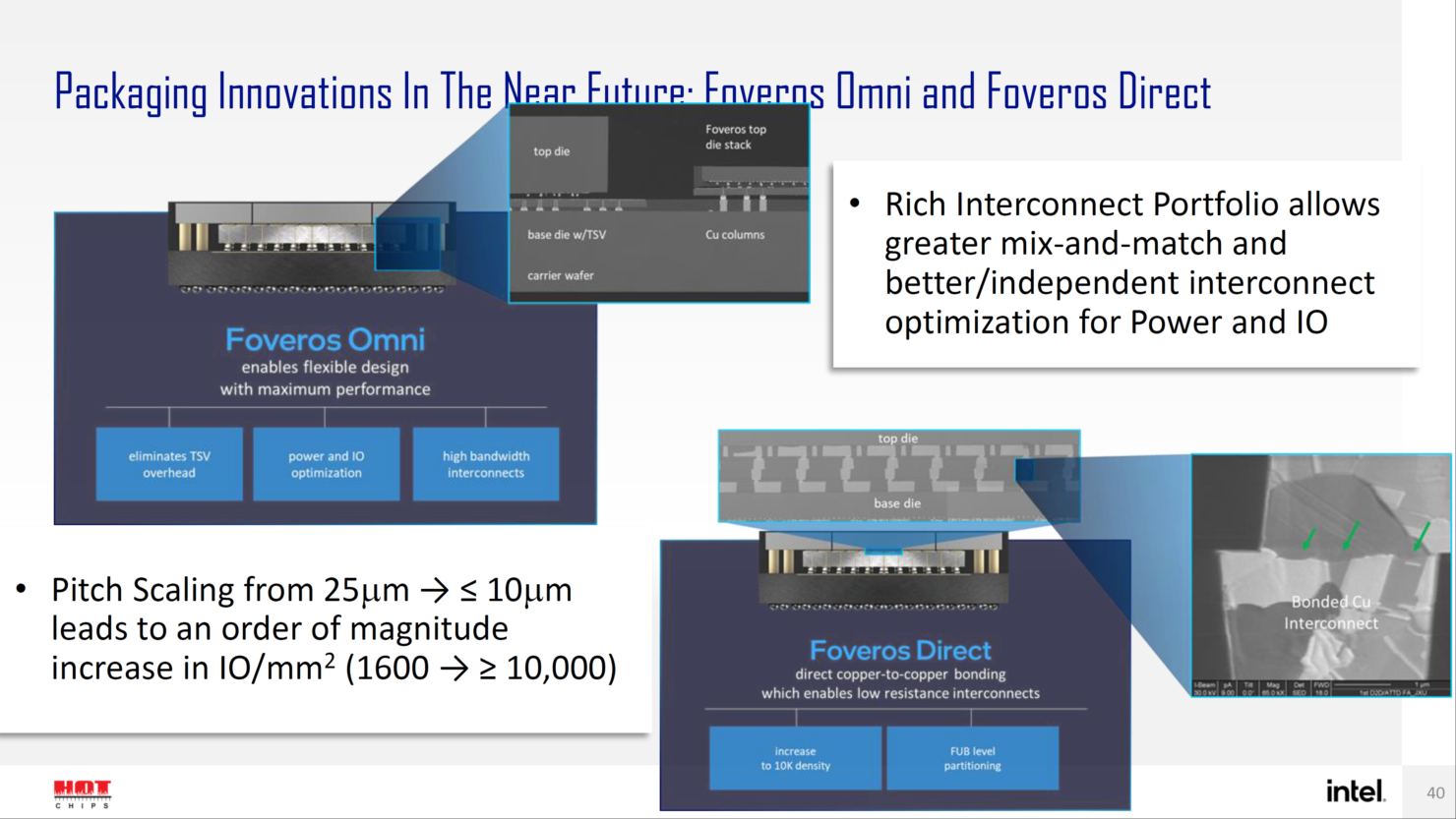

展望未來隨著Forveros Omni和 Forveros Direct進入電晶體管開發的埃時代,Intel將擁有多種用於高級封裝設計的下一代解決方案。