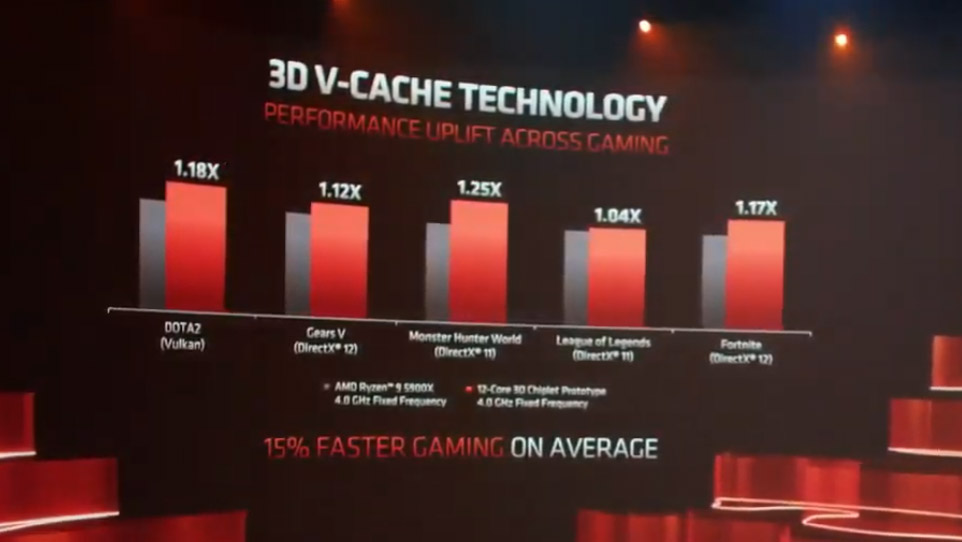

AMD 展示 3D V-Cache 垂直堆疊快取技術可帶來平均 15% 遊戲效能提升

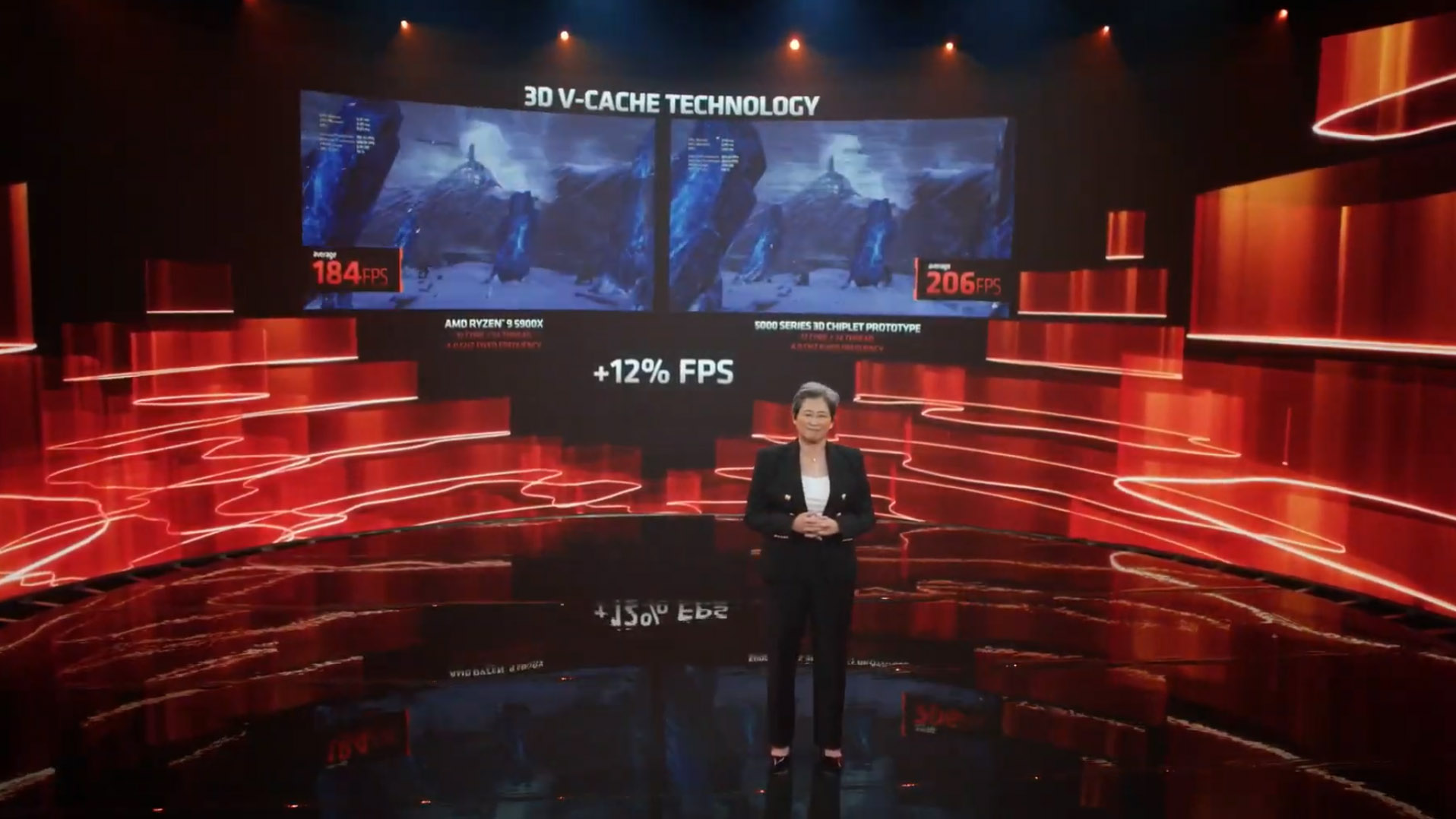

AMD CEO Dr. Lisa Su 於 COMPUTEX 2021 主題演講中,首次展示 AMD 3D Chiplets、3D V-Cache 垂直堆疊快取技術,更可帶來平均 15% 遊戲效能提升。

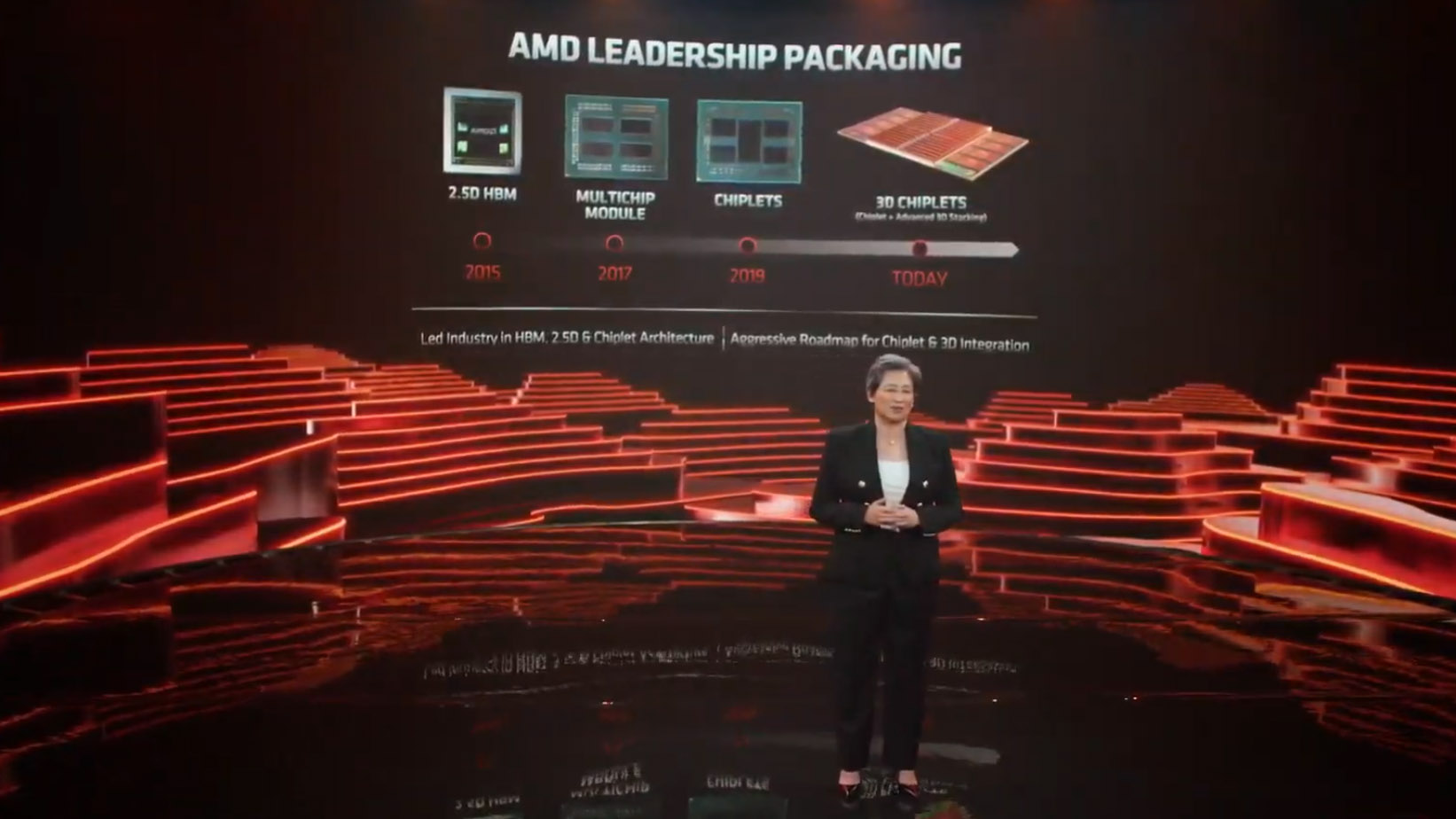

AMD 自 Ryzen 推出之際,就以 Multichip 模組來打造處理器,而在 2019 年則以 Chiplets 設計,讓 CPU 核心配置更有彈性,並將核心與 I/O 功能獨立於不同晶片。

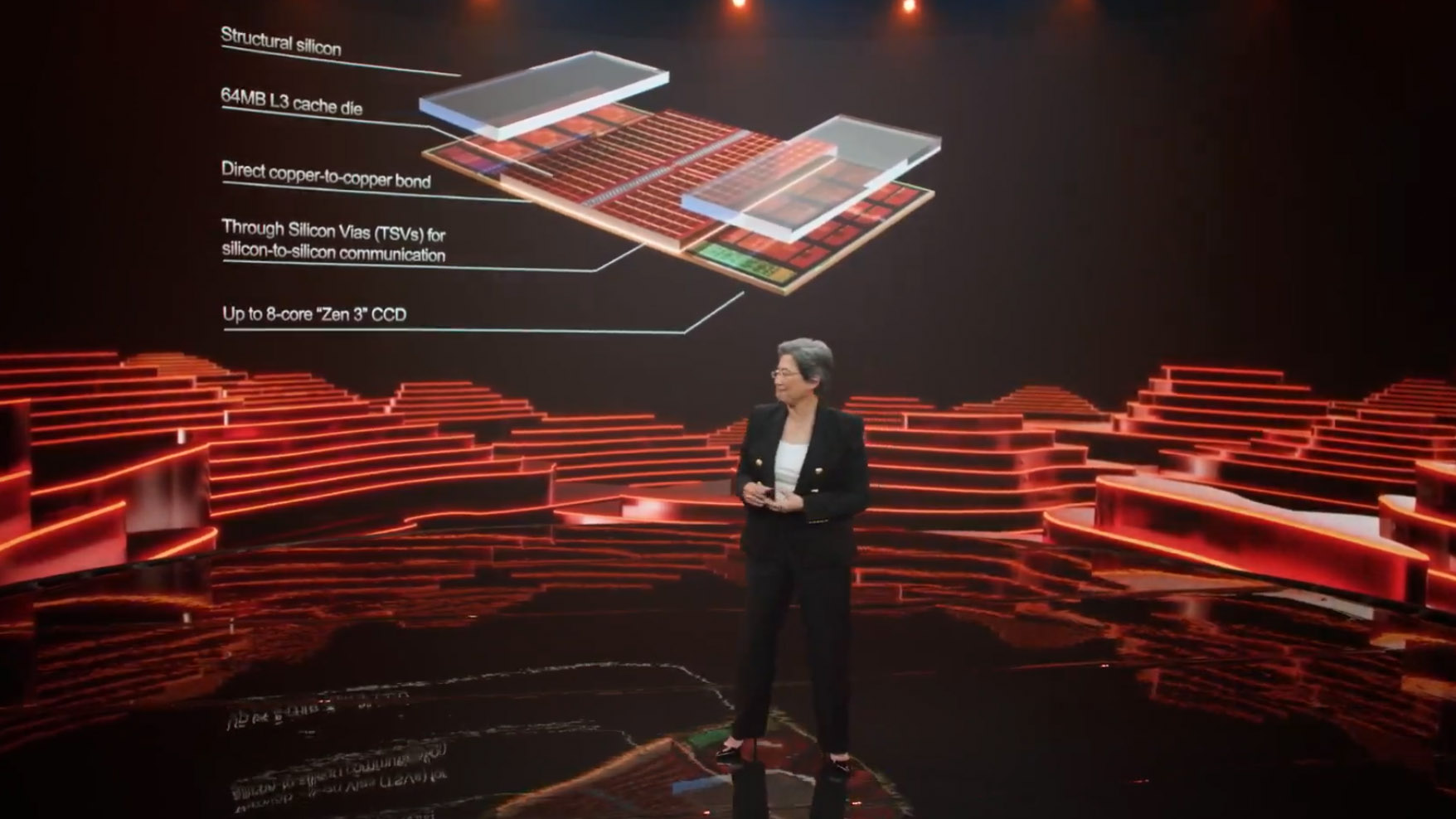

今天 AMD 將與 TSMC 合作 3D Chiplets 堆疊技術,將原本的 CCD 的核心上,垂直堆疊「64MB L3 Cache die」,並採用 Direct Copper-to-Copper bond 直接黏接,而 CPU 核心可直接通過矽穿孔的 Through Silicon Vias(TSVs)直接存取快取資料(silicon-to-silicon communication)。

但 AMD 並沒有透露太多規格,現在單 1 顆 CCD 既有 64MB L3 快取就在核心之間,若採用 3D Chiplets 技術後,以 3D V-Cache 堆疊的快取則成為核心的樓上鄰居,而這封裝技術還可帶來平均 15% 的遊戲效能提升。

究竟是如何藉由封裝改變後讓處理器可有更快的快取速度,進而提升整體的遊戲效能,只能期待今年底 AMD 首次發表 3D Chiplets 的 Ryzen 或 Threadripper 處理器了。