Intel:摩爾定律不會過時,全球首發10奈米技術

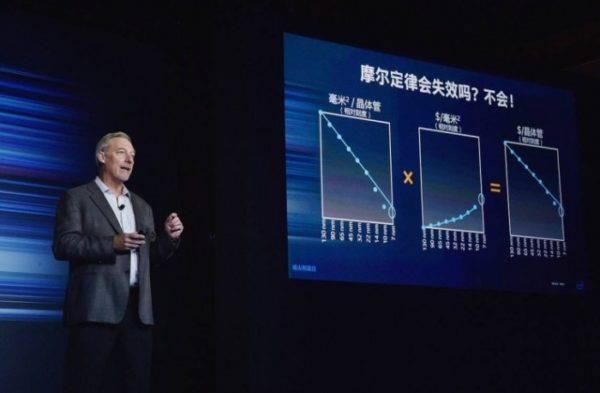

摩爾定律失效了嗎?這是最近幾年被反復提及的一個問題。自從 1965 年提出到現在,摩爾定律一直在沿著半導體製造技術不斷增強的方向前進,但是到了 10 奈米時代,業界有不少聲音認為摩爾定律已經逼近相應的物理極限,並將因此而失去效用。然而,在舉行於 9 月 19 日的“英特爾精尖製造日”上,這家半導體行業的領軍者針對以上問題給出了自己的答案。

Intel:摩爾定律不會過時

會上,Intel 執行副總裁兼製造、營運和銷售集團總裁 Stacy Smith 對摩爾定律的意義進行了強調。他表示,按照摩爾本人的觀察,晶片上的電晶體數量每隔 24 個月將增加一倍;也就是說,在半導體行業產品的性能每兩年翻一倍,每個電晶體成本也隨值下降。但是 Intel 認為,摩爾定律其實反映的是這樣一個經濟學原理:

按照特定節奏推動半導體製造能力的進步,我們就可以降低任何依賴於計算的商業模式的成本。

Smith 表示,目前業界經常用 16 奈米、14 奈米、10 奈米等製程節點數字來衡量半導體行業的工藝發展,這些數字的確曾經有它真實的物理意義,但現在卻並非如此。實際上,Smith 給出了另外一個衡量性能的指標:電晶體密度。

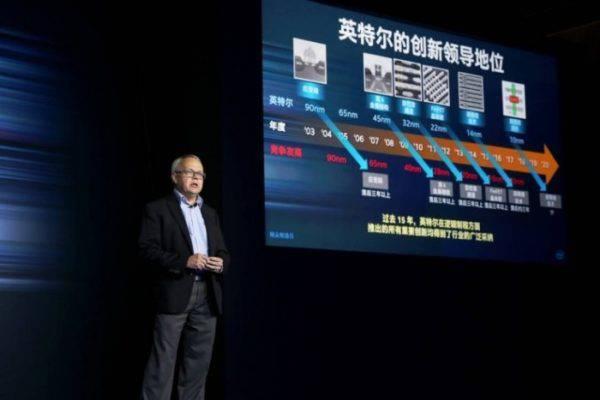

因此,為了提升電晶體密度,在推動製造技術推進的同時,Intel 在 14 奈米制程中採用了鰭式場效應電晶體(FinFET)和超微縮技術(Hyper Sacling),其中超微縮技術能夠讓 14 奈米和 10 奈米上的晶片面積縮小了 0.5 倍以上。

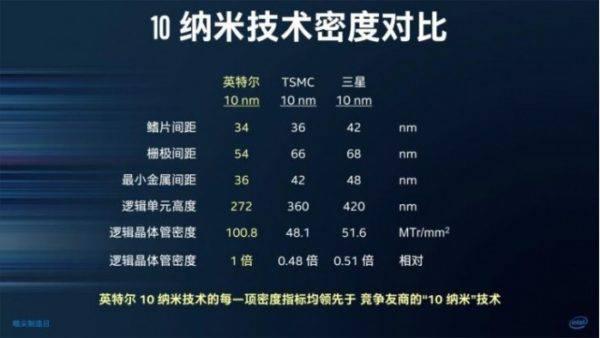

針對市場上競爭對手用 14奈米、10奈米等製程節點數字來凸顯優勢的現象,Smith 也表示不屑。他表示,雖然數位變了,但在 FinFET 的技術上競爭對手產品的電晶體密度並沒有提升;實際上,三星、台積電友商 10 奈米製程技術的電晶體密度只相當於 Intel 14 奈米製程的電晶體密度,並且前者推出的時間還比 Intel 晚了三年。

而在 14 奈米製程之外,Intel 的 10 奈米技術也將量產,並且也用上了超微縮技術。Smith 還表示,實際上 Intel 一般要求自己前瞻三代製程,目前已經在探索 7 奈米和 5 奈米製程。

Smith 最後強調稱,摩爾定律在任何可預見的未來都不會終結。

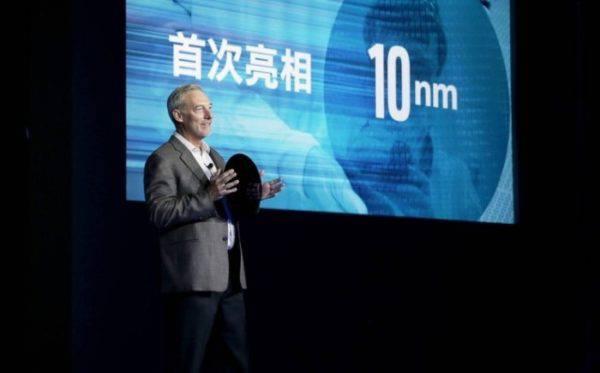

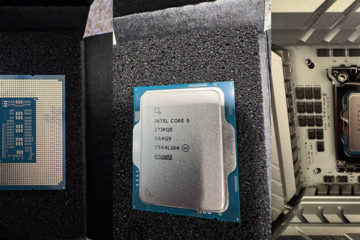

10 奈米晶圓全球首發,即將量產

在本次“英特爾精尖製造日”上,Intel 面向全世界首次展示了 10 奈米 Cannon Lake 晶圓。Intel 高級院士兼技術與製造事業部製程架構與集成總監 Mark Bohr 上臺對摩爾定律和 10 奈米晶圓進行了補充介紹。

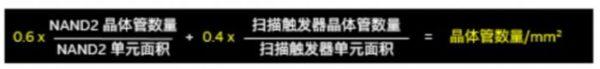

Bohr 首先提出了一個更加量化的、用來計算電晶體密度的公式:

這個公式用到了兩個邏輯概念,一個是 NAND 單元,一個是掃描觸發器邏輯單元。用 NAND2 電晶體數量除以 NAND2 單元面積,即 NAND 密度;用掃描觸發器電晶體數量除以掃描觸發器單元面積,得出其密度;前者乘以 0.6 係數,後者乘以 0.4 係數,相加之後即電晶體每平方毫米的數量,也就是電晶體密度。

Bohr 表示,如果用這種方法計算,10 奈米在電晶體密度上的提升是非常明顯的,為自家 14 奈米技術的 2.7 倍,大約是業界其他家“10 奈米”工藝的 2 倍。而這一提升,就得益於 Intel 的超微縮技術。實際上,Intel 10 奈米製程的最小柵極間距從 70 奈米縮小至 54 奈米,且最小金屬間距從 52 奈米縮小至 36 奈米,尺寸的縮小使得邏輯電晶體密度可達到每平方毫米 1.008億 個電晶體。

相比之前的 14 奈米製程,英特爾 10 奈米製程提升高達 25% 的性能和降低 45% 的功耗。增強版的 10 奈米製程可將性能再提升 15% 或將功耗再降低 30%。

Bohr 也表示,摩爾定律的目標是提供電晶體的密度,並通過每一代的代際提升來降低成本,從而降低每一個電晶體的平均成本。而從 Intel 10 奈米晶片技術的出現,也恰好說明了摩爾定律沒有過時,一直在向前發展。

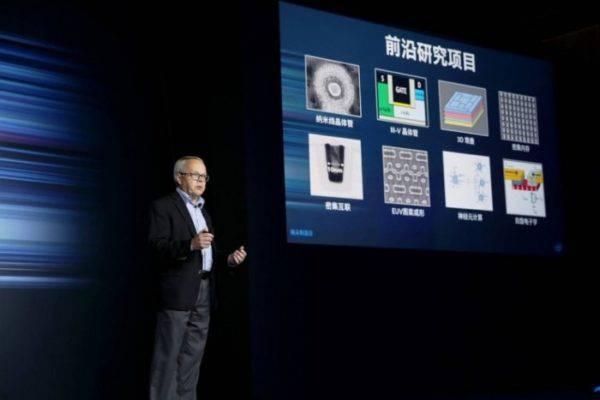

其實,Intel 還有晶圓代工業務

除了對前沿晶片技術進行不斷探索,Intel 其實也在數年前推出了自己的晶圓代工業務,目前也已經進軍中國市場;而在此次“英特爾精尖製造日”上,負責晶圓代工業務的 Intel 技術與製造事業部副總裁 Zane Ball也對晶圓代工業務進行了介紹。

Ball 表示,Intel 的晶圓代工的優勢在於技術。這首先表示在 FinFET 技術,目前 Intel 已經出產了 700 萬片採用這一技術的晶圓;其次是 22 奈米、14 奈米、10 奈米和 22FFL 等製程技術。

其中 Ball 對 Intel 的 22FFL (22 奈米 FinFET 低功耗)技術進行了重點強調。據雷鋒網瞭解,22FFL 是在 2017 年 3 月美國“英特爾精尖製造日”活動上首次宣佈的一種面向移動應用的超低功耗 FinFET 技術,其技術基礎是 Intel 的 22 奈米/14 奈米的製造經驗。

與先前的 22GP(通用)相比,22FFL 技術的漏電量最多可以減少 100 倍,可以提供主流技術中漏電量最低的電晶體。它還可以達到 Intel 14 奈米電晶體相同的驅動電流,實現比業界 28 奈米/22 奈米平面技術更高的面積微縮。

22FFL 在技術上的另一個特點是高集成度;它包含一個完整的射頻(RF)套件。借由廣泛採用單一圖案成形及簡化的設計法則,使 22FFL 成為價格合理、易於使用可面向多種產品的設計平臺,與業界的 28 奈米的平面工藝 (Planar) 相比在成本上極具競爭力。

相對而言,22FFL 新技術適用於低功耗的物聯網和移動產品,它將性能、功耗、密度和易於設計的特性結合起來。Intel 副總裁 Stacy Smith 也針對 22FFL 表示:

我們認為這是業界最簡單易用的 FinFET工藝,服務大眾的 FinFET。

基於以上技術優勢,Intel 的晶圓代工業務主要分為兩個市場:一個是網路基礎設施,比如說網路處理器、FPGA;另外一個是移動和聯網設備,尤其是入門級的智慧手機處理器和物聯網設備。

作為晶圓代工業務的一個案例,Intel 與 ARM 進行了合作,將 ARM Cortex A75 放到 Intel 標準的晶圓代工流程當中。整個過程由 ARM 提供 IP,用了 14 周時間就完成了首個流片。這個流程採用了 Intel 的 10 奈米晶圓代工技術,檢測頻率至少可以超過 3.3 GHz;而且從展示的資料看,顯得非常穩定。

在現場,Intel 還與 ARM 合作展示了全球首款採用 Intel 10 奈米製程的 ARM Cortex-A75 CPU 內核測試晶片。

老虎不說話,你當我是病貓呀

過去 Intel 給人的印象是主攻技術,非常低調;但此番 Intel 專門設置了一個所謂的“精尖製造日”來宣傳自己的新技術,並且正面對上了三星、台積電等競爭對手。對此,Intel 中國區總裁楊旭的回應是“老虎不說話,你當我是病貓呀”。

不過,實際上,本次“精尖製造日”的宣傳重點其實是 Intel 的晶圓代工業務,尤其是針對中國市場。不過雷鋒網認為,Intel 之所以如此高調,實際上還是看到了中國半導體行業蓬勃發展的狀況。在 58.5% 的全球半導體消費都發生在中國的情況下,Intel 自然也希望通過晶圓代工業務從中分一杯羹。不過從眼下來看,晶圓代工業務只是 Intel 整體業務很小的一部分。

至於“摩爾定律是否失效”這個問題,Intel 也罕見地拿出了高調的姿態為之正名,並試圖通過 10 奈米製程技術和其他的一些前沿技術來說明它的長期有效性。

在雷鋒網看來,至少目前說“摩爾定律已經過時”還為時過早,我們也期待在半導體行業在各種前沿新技術的推進下繼續向前發展。