AMD 針對 I/O 密集且注重成本的邊緣應用推出 Spartan UltraScale+ 系列 FPGA

AMD 推出 Spartan UltraScale+ 系列 FPGA,採用更新製程並具有更低的功耗與高 I/O 邏輯比率,可為各種 I/O 密集型邊緣應用提供成本效益與能源效率。

近來 FPGA (Field Programmable Gate Array, 可程式化邏輯閘陣列)應用面更多,包括人工智慧、嵌入式視覺、工業網路、機器人、低功耗的邊緣運算應用…等等,使得市場上有更多的產品選擇。

看好 FPGA 的表現,AMD 在 2022年併購以 FPGA 產品知名的賽靈思(Xilinx),現在針對低功耗的邊緣應用,AMD 宣布推出具有成本最佳化的 Spartan UltraScale+ FPGA 系列新產品。Spartan UltraScale+ 為各種 I/O 密集型的邊緣應用提供成本效益與能源效率,並具有最強大的安全功能組合。

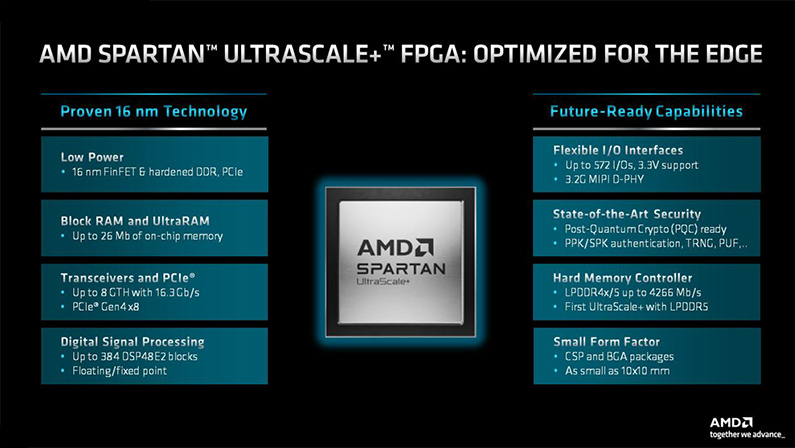

Spartan UltraScale+ FPGA 具有體積小、更低功耗、更高安全性及更多 I/O 數等特色

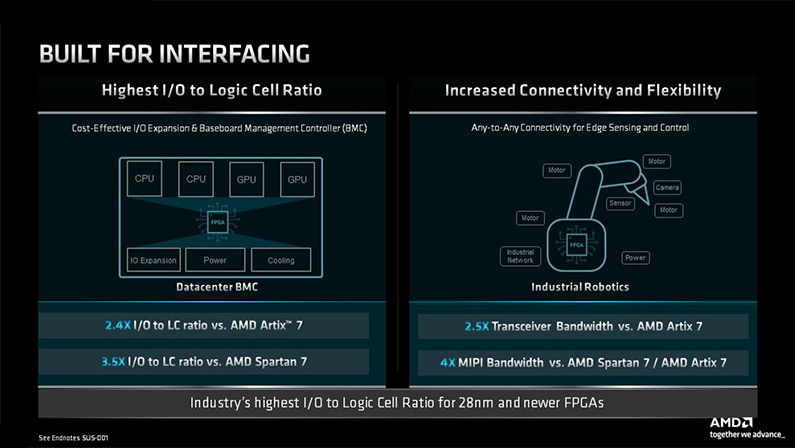

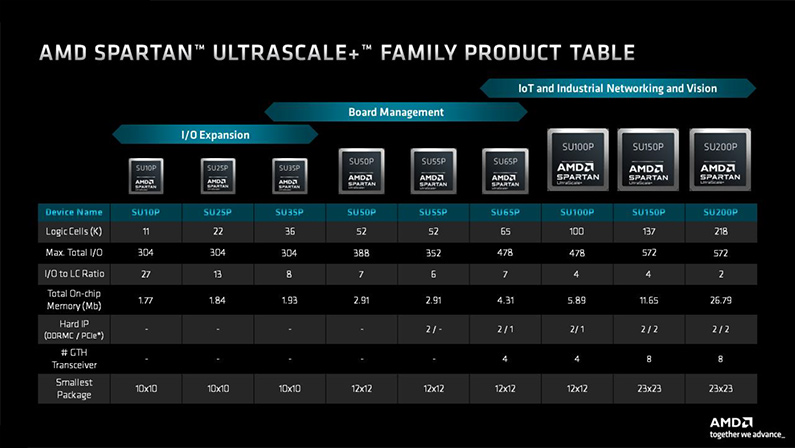

Spartan UltraScale+ FPGA 為邊緣進行最佳化,提供高 I/O 數量和靈活的介面,使 FPGA 能無縫整合並有效地與多個裝置或系統接合,以應對感測器和連接設備的爆炸式成長。

和之前的產品相比,Spartan UltraScale+ FPGA 系列擁有更多的 I/O 數, 也擁有更高的傳輸及 MIPI 頻寬

針對物聯網等邊緣應用,Spartan UltraScale+ FPGA 是現今 28nm 以下製程相關產品中擁有最高的 I/O 邏輯單元比率,系列產品當中最多具有 572個 I/O 並支援 3.3V的電壓,以便連接各種邊緣感測和支援控制應用。此系列產品採用經驗證的 16nm 製程,並提供不同的封裝選擇,最小為 10x10mm,以便在空間限制較多的環境中提供高 I/O 密度。AMD FPGA 廣泛的產品組合可提供擴展性,從成本最佳化 FPGA 到中、高階產品。

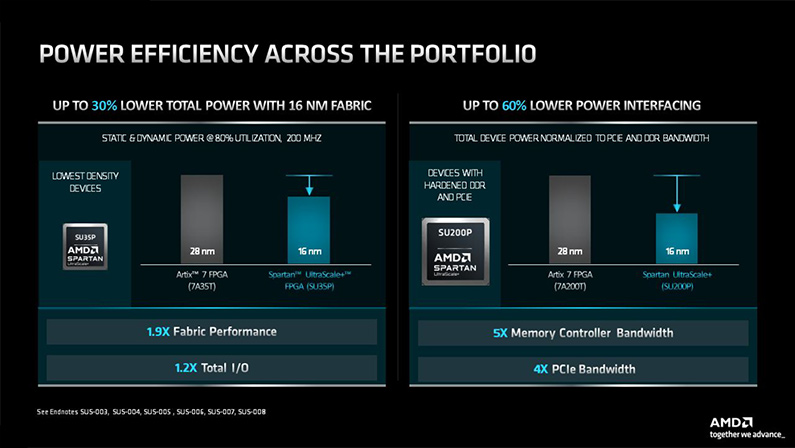

採用 16nm 製程的 Spartan UltraScale+ FPGA 系列擁有更佳的能源使用效率

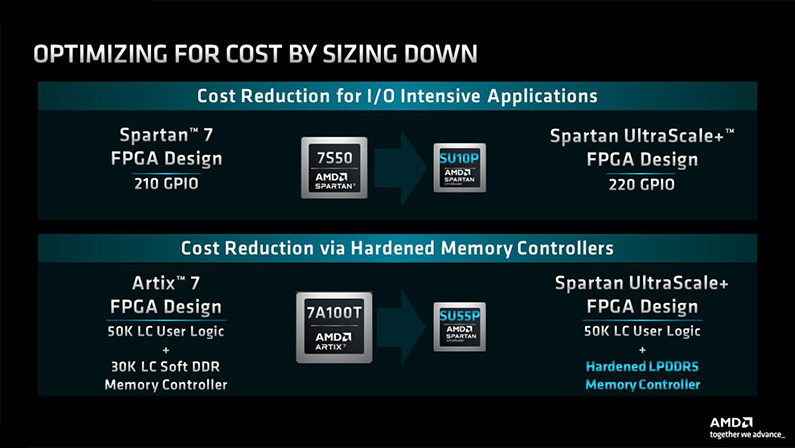

Spartan UltraScale+ FPGA 系列體積更小卻擁有硬體化記憶體控制器與高 I/O 數

Spartan UltraScale+ 系列採用 16nm FinFET 製程技術與硬體連接功能,比過去採用 28nm 的 Artix 7系列,預估功耗可降低高達30%。AMD UltraScale+ FPGA 也是首款具有硬體化 LPDDR5 記憶體控制器和 PCIe Gen4 x8 介面,可滿足能源效率與未來的不同需求。

在極為重視資訊安全的今日,Spartan UltraScale+ FPGA 系列是 AMD 成本最佳化 FPGA 產品組合中具有最佳的安全功能。Spartan UltraScale+ FPGA 支援後量子密碼技術,並具有 NIST 認可的演算法,可提供最先進的智慧財產(IP)保護,並能對抗不斷演變的網路攻擊和威脅。實體無法複製功能(PUF)則為每個設備提供唯一的指紋以增加安全性。

而且還具有 PPK/SPK 金鑰支援有助於管理過時或受到威脅的安全金鑰,差異化功耗分析有助於防止旁通攻擊,另外還具有永久的篡改處罰設計,以進一步防止誤用。此外還有強化的單粒子翻轉( Single-Event Upset)效能有助於進行快速、安全的配置,並提升可靠性。

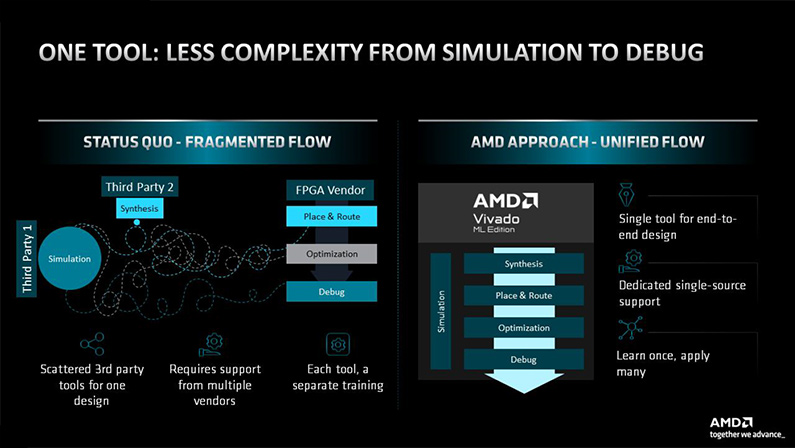

可運用 AMD Vivado 設計套件和 Vitis 統一軟體平台降低開發的複雜度

為了減少開發人員的負擔以及流程的複雜性,開發時不須使用各種不同廠商的開發工具,AMD FPGA 和自行調適 SoC 產品組合可採用 AMD Vivado 設計套件和 Vitis 統一軟體平台,讓硬體與軟體設計人員能透過從設計到驗證的單一設計工具,充分發揮工具以及生產力。

AMD Spartan UltraScale+ FPGA 系列提供多種產品組合可供選擇

AMD Spartan UltraScale+ FPGA產品系列的樣品和評估套件預計於2025年上半年推出,相關文件已開始提供,AMD Vivado 設計套件將於2024年第四季起提供工具支援。