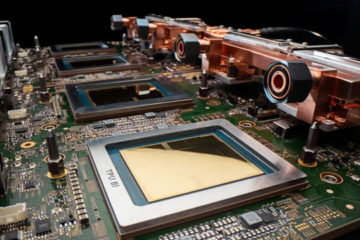

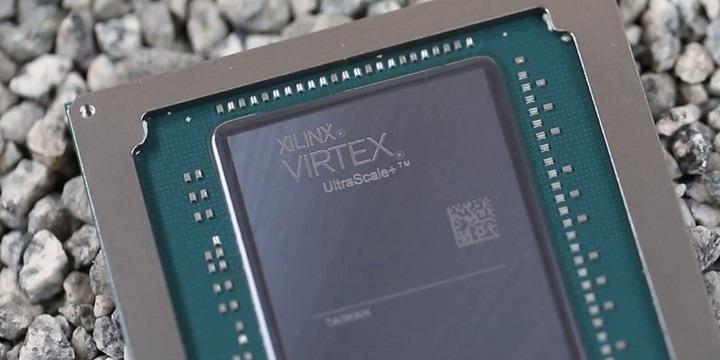

賽靈思 (Xilinx) 宣布推出史上最大的 Virtex UltraScale+ VU19P FPGA 晶片

全球最大的電場可程式化邏輯閘陣列 (FPGA) 大廠賽靈思 (Xilinx),宣布推出史上電晶體最多的

Virtex UltraScale+ VU19P FPGA。製程上採用台積電相對成熟的 16 奈米製程,擴展旗下 16 奈米 Virtex UltraScale+ 系列。

VU19P內含350億個電晶體,為史上單顆元件上最高的邏輯密度與 I/O 數的 FPGA,可提供客戶進行特殊專一應用晶片 (ASIC)、系統單晶片 (SoC) 的開發模擬測試。在規格方面,VU19P 擁有 900 萬個邏輯單元、每秒 1.5 Tb 的 DDR4 記憶體頻寬、高達每秒 4.5 Tb 的 Transceivers 頻寬及 2,072 個 I/O。不但能促成現今最複雜 SoC 的原型開發與模擬,還能支援各種複雜的新興演算法的開發,包括用在人工智慧 (AI)、機器學習 (ML)、影像處理及等領域的演算法進行 accelerator。

圖片來源 : Xilinx

賽靈思產品線行銷與管理資深總監 Sumit Shah 表示,VU19P 不僅能協助開發者加速硬體驗證,還能助其在 ASIC 或 SoC 可用之前就率先進行軟體整合。這是賽靈思刷新世界紀錄的第三代 FPGA;前兩代分別為 Virtex-7 2000T 與 Virtex UltraScale VU440,現在則推出 Virtex UltraScale+ VU19P。但是,伴隨此次新產品發布的,不僅僅是精進的晶片技術,我們還為之提供了穩定且經驗證的工具與IP支援。

透過一系列廣泛的除錯 (debug)、可視性工具 (visibility tools) 與 IP 支援,VU19P 為客戶快速設計與驗證新一代的應用與技術,提供了一個全方位的開發平台。軟硬體的協同驗證讓開發者能在取得實體元件前,就先著手軟體與客製化功能的建置。此外,透過運用賽靈思 VivadoR 設計套件能協同最佳化設計流程,以降低成本與投片風險、改善效率並縮短上市時程。

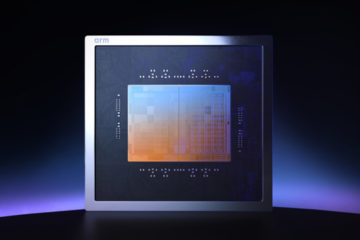

ARM 設計服務總監 Tran Nguyen 表示,ARM 仰賴賽靈思元件作為驗證新一代處理器 IP 與 SoC 技術的工藝。新推出的 VU19P 將進一步支援 ARM 及我們的產業生態系中的業者,加速實現設計、研發與驗證我們最遠大的技術發展藍圖。VU19P 預計將於 2020 年秋季開始全面供貨。