AMD 有望將 3D 堆疊 SRAM 和 DRAM 用於其 CPU 和 GPU

Intel 在去年 12 月的“架構日”活動上公佈了名為“ Foveros ”的全新 3D 封裝技術,該技術首次引入了 3D 堆疊的優勢,可實現在邏輯晶片上堆疊邏輯晶片,當時 Intel 展出使用該技術製造的 Hybrid x86 CPU ,也公佈了一些規格細節。老對手 AMD 當然也不甘落後, AMD 在最近的活動中透露,他們正致力於在其處理器之上使用 3D 堆疊 DRAM 和 SRAM 的新設計來提高性能。

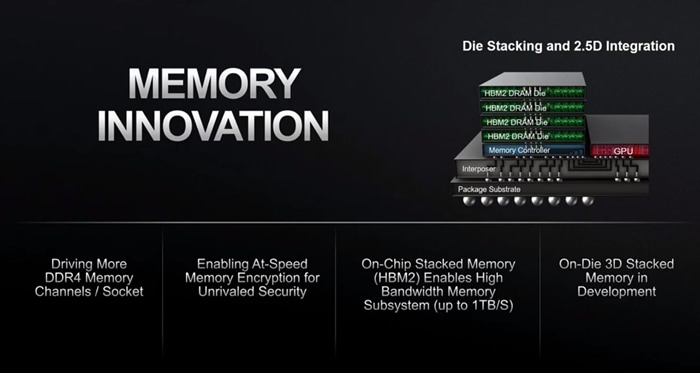

AMD 高級副總裁 Norrod 最近在 Rice Oil and Gas HPC 會議上發表談話,並透露該公司正在進行自己的 3D 堆疊技術,角度與 Intel 的略有不同。在此之前 AMD 已經將 HBM2 記憶體堆疊在其 GPU 核心旁邊,這意味著它與處理器位於同一個封裝中,但該公司計畫在不久的將來轉向真正的 3D 堆疊。Norrod 解釋說, AMD 正致力於在 CPU 和 GPU 之上直接堆疊 SRAM 和 DRAM 記憶體,以提供更高的頻寬和性能。

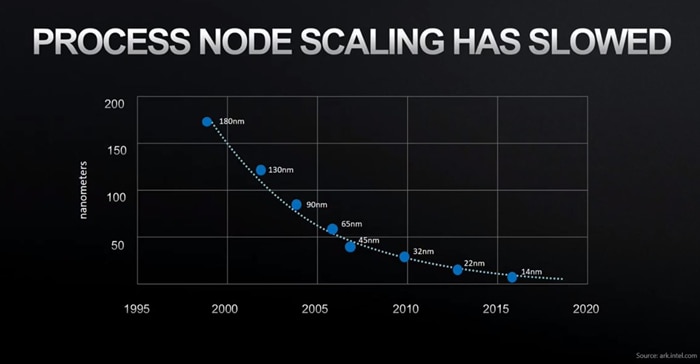

顯然這種創新已經成為必然的選擇,因為摩爾定律已經失效,多年來業界一直在追求提升半導體工藝不斷降低線寬,但是線寬的微縮總是有一個極限的,到了某種程度,就沒有經濟效應,因為難度太大了。 Norrod 在會議中也說到,該行業正在達到積體電路微縮的極限。即使是像 Threadripper 處理器這樣的多晶片設計,由於處理器封裝的尺寸已經非常龐大,也會遇到空間限制的阻礙。

與許多半導體公司一樣, AMD 已經調整了應對這新困難的戰略,同時也步入下一個新的浪潮: 3D 堆疊晶片技術。不過由於熱量和功率輸送限制,該方法也帶來了挑戰。 Norrod 沒有深入探討正在開發的任何設計的具體細節,但這很可能是 AMD 處理器設計的一個歷史性節點。