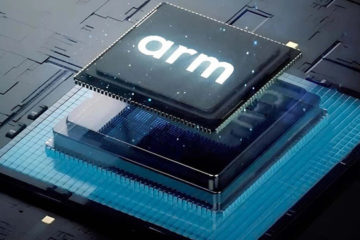

AMD 新影片說明使用 3D V-Cache 技術的 Zen 3+ 架構

AMD 藉由 YouTube 影片來說明新的 3D V-Cache 技術與即將到來的 Zen 3+ 處理器。

AMD 在 COMPUTEX 2021 發表 3D V-Cache 技術採用 TSMC SoIC stacking 堆疊技術,讓晶片可往 Z 軸堆疊而非只能增加 X 軸的面積。而當時展示的是 Ryzen 9 5900X 12-Core 處理器的原型,並在每個 CCX 當中增加 64 MB L3 cache 快取,基本上就是增加 CPU 的 3 倍 L3 快取量,更可增加遊戲 FPS 約 15%

而 AMD 並非採用 microbump 的堆疊技術,而是將上層的 L3 cache 與下層的 CCX 核心對齊,直接採用 TSVs (Through Silicon Vias) 通孔連接;而為了達到這設計,AMD 將 CCX 晶片上下顛倒,並消除多餘的 silicon 後直接堆疊 3D V-Cache 裸晶。

最終可讓 CPU 存取 L3 快取的時間縮短,藉由 zero-gap 的堆疊,讓核心存取 Z 軸快取比起以往 X 軸的快取還快,通過這點達到功耗優化、提升效能;有興趣的玩家可參考 AMD 影片。

source: techpowerup.com