Intel PowerVia 背部供電有效提升電晶體密度並通過測試預計 2024 年 20A 製程節點推出

Intel 的半導體製程研發已證實 PowerVia 背部供電設計能有著更好的供電與頻率優勢,並將於 2024 上半年在 Intel 20A 製程節點推出。藉由將電源迴路移至晶圓的背面,解決因晶片面積微縮而日益嚴重的互連瓶頸問題。

Intel 的 PowerVia 晶片設計,是將連接電晶體的電源線和訊號線架構分離,尤其對於電晶體微縮有著相當大的幫助,讓晶片設計人員能夠在毋須犧牲資源的情況下提升電晶體密度,提供相較過往更高的功率和效率。

Intel 20A 和 Intel 18A 均會導入 PowerVia 背部供電技術和 RibbonFET 環繞式閘極技術。作為一款全新的電晶體電源傳輸方式,背部供電實作也向散熱和除錯設計提出新的挑戰。

藉由將 PowerVia 的開發與 RibbonFET 脫鉤,Intel 可以迅速地解決這些挑戰,確保在 Intel 20A 和 18A 製程節點晶片實作時已做好萬全的準備。Intel 工程師開發出避免散熱問題的緩和技術,除錯小組也發展出新技術,確保新款設計結構能夠被正確除錯。

實作測試的結果顯示出穩定的良率和可靠性指標,於整合 RibbonFET 架構之前就展現出該技術優秀的內在價值。

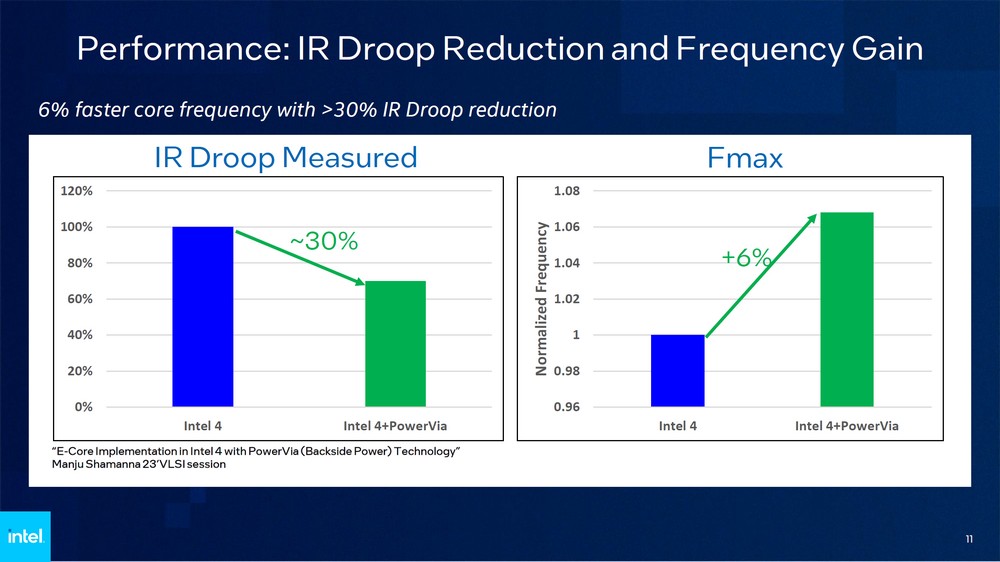

該測試還利用 EUV(極紫外光)微影的設計規則,其結果包含在晶片大面積上達成超過 90% 的標準單元利用率,提升單元密度同時降低成本。本測試還顯示出平台電壓下降幅度改善超過 30% 以及 6% 的頻率優勢。英特爾也迎合邏輯單元微縮隨之而來的高功率密度,在 PowerVia 測試晶片達成所需散熱特性。

source: intel.com