Intel未發布的6核心處理器擁有有趣的快取設計,可能暗示了新架構

SiSoftware Sandra資料庫中出現了未發布的Intel處理器 ,儘管該6核處理器可能看起來像常見晶片,但其快取設計卻指向了全新的架構設計。關於Intel 14nm 處理器的backporting的傳聞不斷,有可能這可能是Core或Xeon市場的下一代產品。

因此談論這6個核心部分的細節時,該處理器有6個核心和12個線程,這沒什麼特別的,因為Intel之前已經發布了6個核心和12個線程的處理器。Core i7 8700K和幾個Xeon產品均提供6個核心和12個線程。第9代Coffee Lake更新系列中沒有多線程6核心產品,但即將推出的第10代Comet Lake-S產品將包含其中的一些。

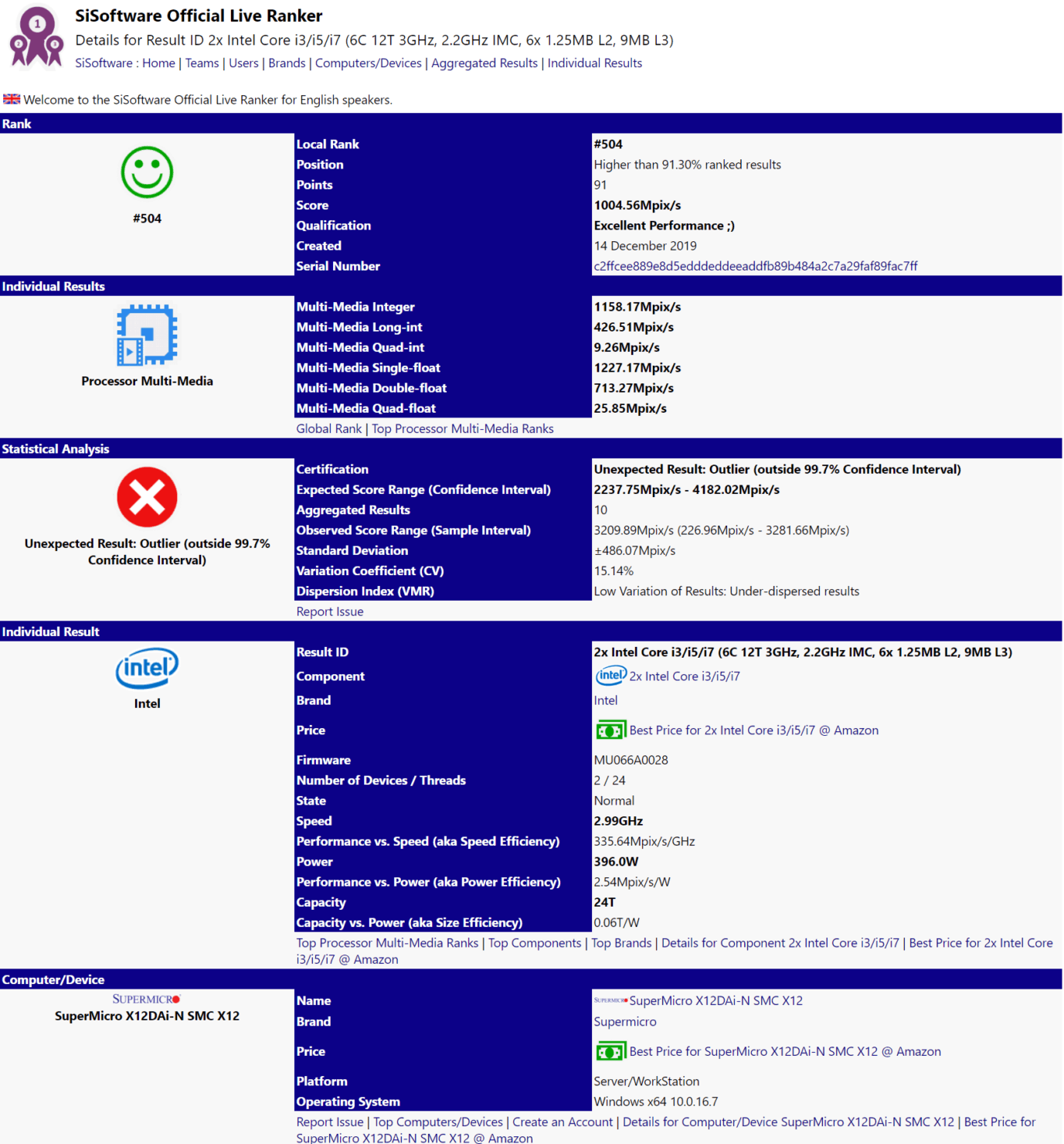

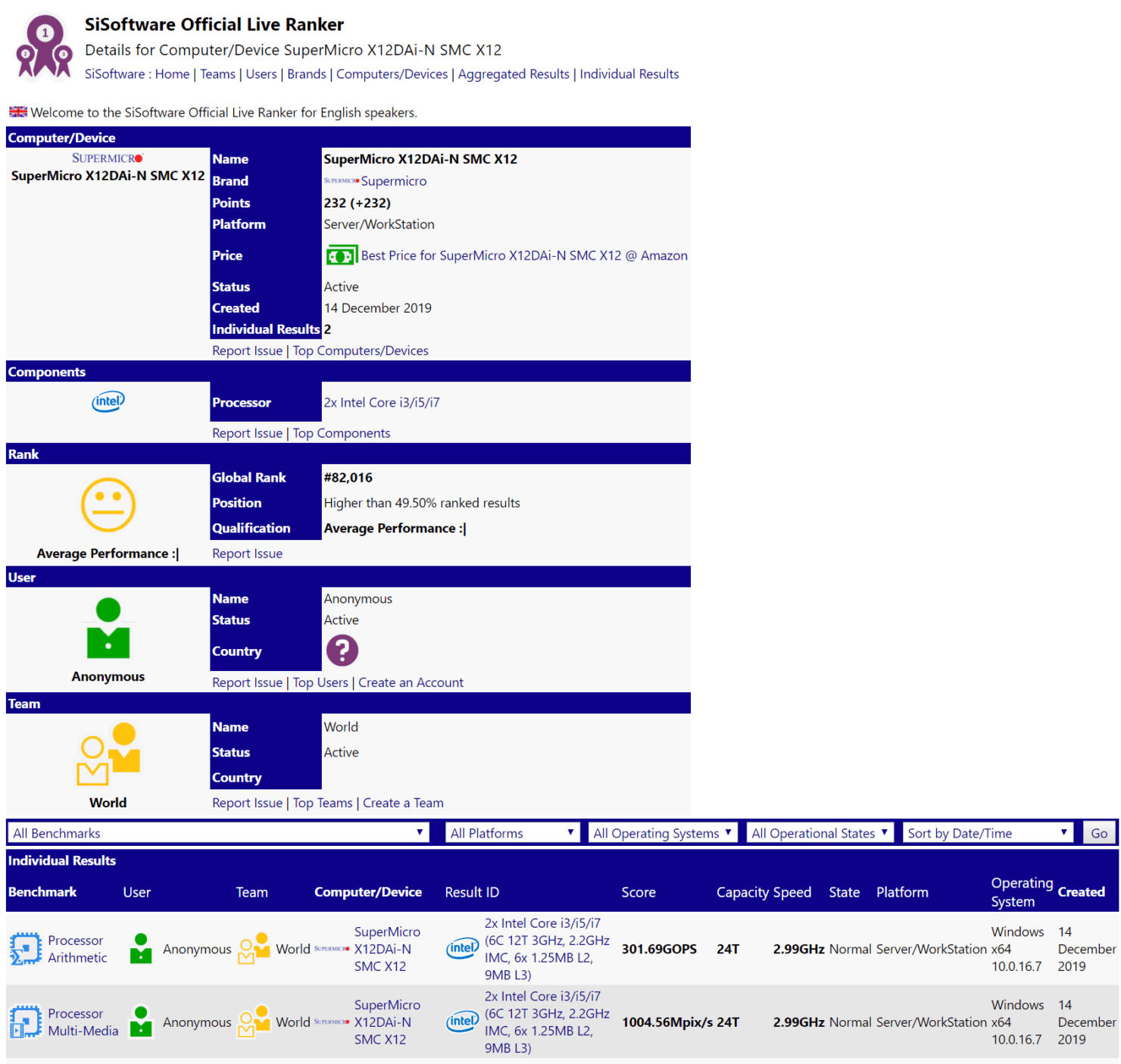

在速度方面,該晶片具有3GHz時脈速度和2.2 GHz IMC。這是相當標準的工程或早期樣品,因為它沒有名稱。但這裡有趣的是據測試該平台是Supermicro的雙插槽設計。

具體平台是SuperMicro X12DAi-N SMC X12。我們沒有該主機板的任何詳細訊息,但明確指出有兩個晶片。由於SiSoftware資料庫將這些處理器檢測為Core系列市場(Core i3 / Core i5 / Core i7)的一部分,而通常被稱為有2S平台支援功能的Xeon產品則會被稱為XEON系列。

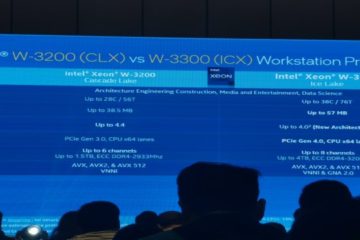

這可能是由於這些晶片的ES特性所致,並且由於不支援這些晶片,因此軟體在正確檢測這些晶片方面感到困惑。下一個重要的細節是該處理器有9MB的L3高速快取,令人驚訝的是每個核心有1.25MB的L2高速快取,在這個6核處理器上有7.5 MB的L2高速快取。這是讓事情變得更加有趣的地方:Intel第9代產品每個核心有256KB的L2快取,Core-X系列每個核心有1MB的L2快取,而10nm Ice Lake CPU則每個核心有512KB的L2快取。

該晶片與L2快取匹配的唯一架構是即將問世的 Tiger Lake系列產品,該產品有與早期Geekbench洩漏中發現的1.25 MB相同的L2快取。Tiger Lake CPU計劃於明年在10nm++製程上推出,並且還將有3MB的升級L3快取,而現有的第9代CPU為2MB,Core-X CPU為1.375 MB。但是L3快取與Tiger Lake架構不匹配,因為每個核心3MB意味著在列出的6個核心部分上有18MB的L3快取,而它僅有9MB的L3快取。

正如有傳言稱這6核晶片很可能是我們將10nm核心架構的backporting到14nm(從Tiger Lake到Rocket Lake)的第一次測試。由於backporting意味著將10nm ++技術轉移到14nm +++,因此我們可能會看到一些變化,例如此洩漏中指出的較小的L3快取設計。否則我們可能只是看到Ice Lake(E)系列中尚未發布的Xeon產品,該產品將於明年上市。