Intel 架構日解密 Alder Lake 的 P core 與 E Core 大小核心更省電效能更達 19% 提升

Intel 架構日於今日解密許多未來新產品的資訊,包含下一代 Alder Lake 所採用的 P core 與 E Core 大小核心、Thread Director 硬體排程單元,以及 Xe HPG 圖形微架構與 XeSS 運用 AI 技術的畫面提升技術。

做為 Intel 下一代筆電、桌上型電腦所使用的 Alder Lake 處理器,其最大特色為具備「效率核心 E core」與「效能核心 P core」,前者以省電出發帶來更有效率的單核效能,而後者則給予更高的多核運算能力。

效率核心 E core

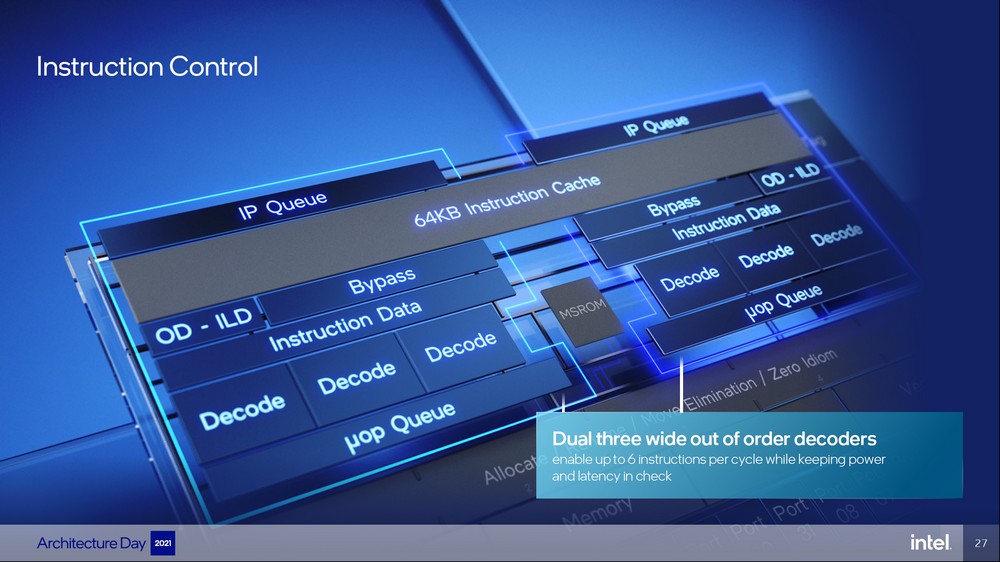

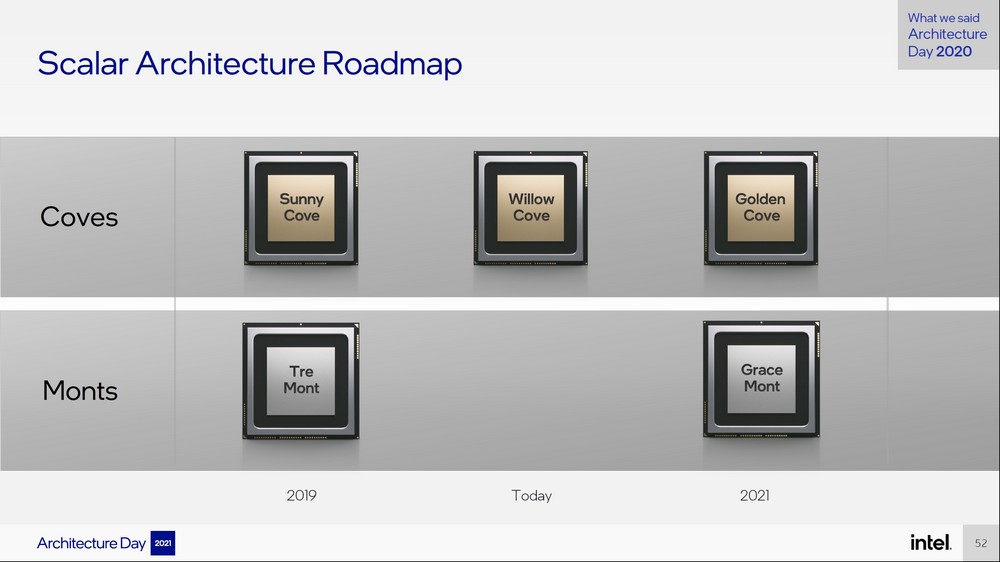

為單執行緒專為吞吐量效率而設計,先前代號稱為「Gracemont」,追求極小化的晶片面積,讓多核心工作負載效能能夠隨著核心數量成長,在核心的 Front End 前端,給予較大的 64KB 指令快取,將有用的指令放在距離較近之處,避免額外產生記憶體子系統的功耗,並有著 5,000 條分支目標快取,達成更為精確的分支預測。

並有著 2 組 3 線寬的 Order Decode 負責解碼每週期可處理 6 個指令,以及寬廣的後端每週期支援 5 條分派(five-wide allocation)和 8 條引退(eight-wide retire),256 條目亂序視窗和 17 個執行埠。

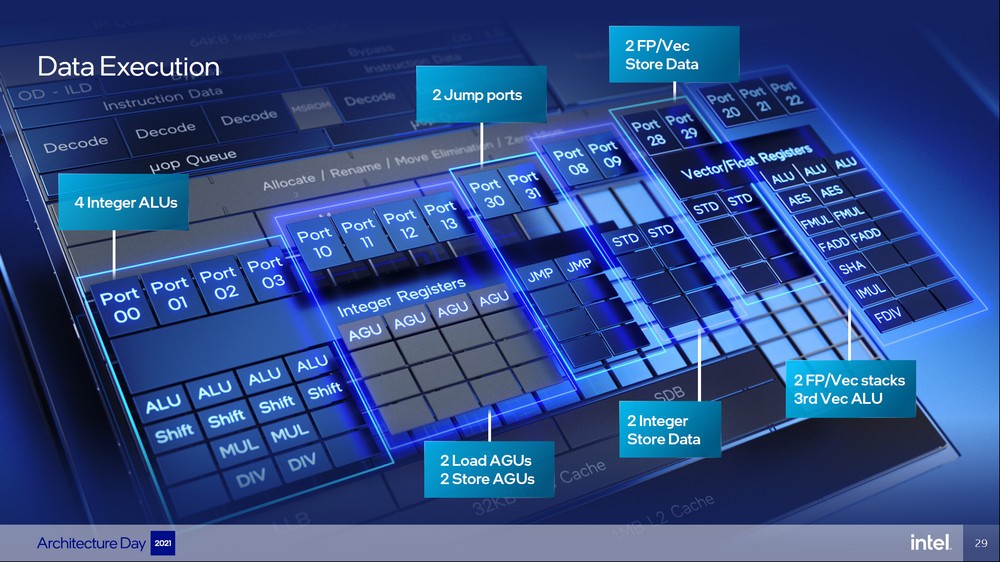

至於核心最重要的 Scalar Engine 與 Vector Engine,則規劃 4 個 ALU、2 個 Load AGU、2 個 Store AGU、2 Jumps Port、2 Integer Store Data,以及 2 個 FP/Vec Store Data 和 2 FP/Vec stacks、3rd Vec ALU 等 17 個執行埠。

記憶體子系統則支援 2 Load、2 Store 操作並有著 4MB L2 快取,以及更深的緩存與先進預取,更通過 Intel Resource Director 技術,讓軟體可公平控制不同核心執行緒。

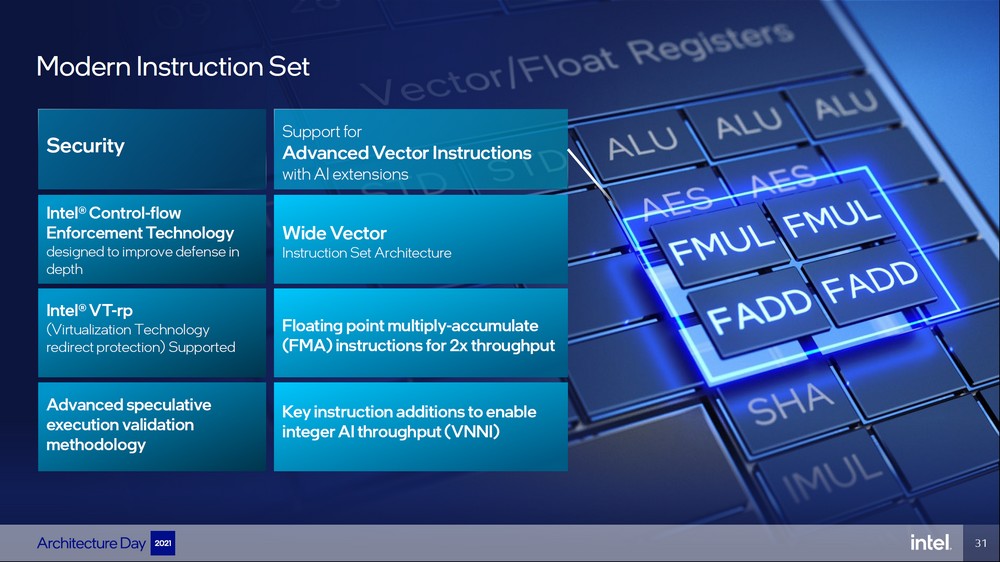

核心也加入現代指令所提供的強式安全功能支援 Intel Control-Flow Enforcement Technology 以及 Intel Virtualization Technology Redirection Protection、FMA、VNNI 等。

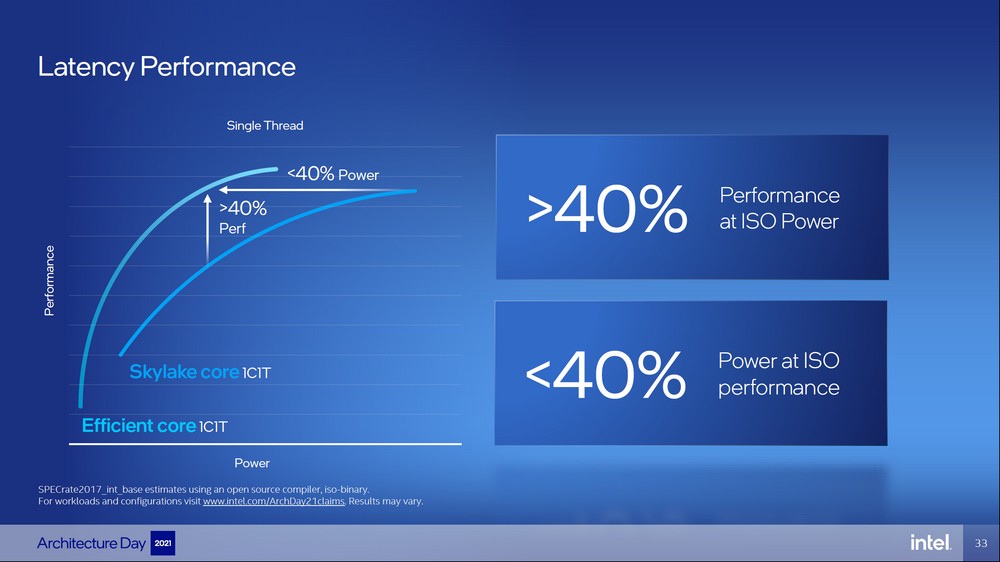

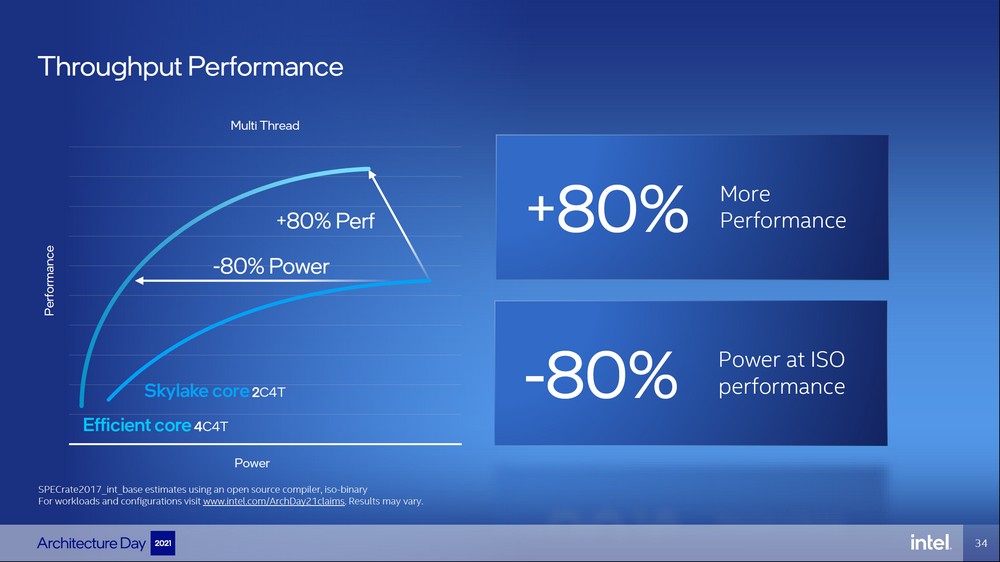

效率核心 E core 與 Intel Skylake CPU 核心相互比較,在 1 Core 1 Thread 測試下 E Core 在相同功耗可多出 40% 效能,或是在同效能下能降低 40% 功耗。多核心 4C4T 測試對上 Skylake 雙核心 2C4T,能在相同功耗下提升 80% 效能,或是在同效能下降低 80% 功耗。

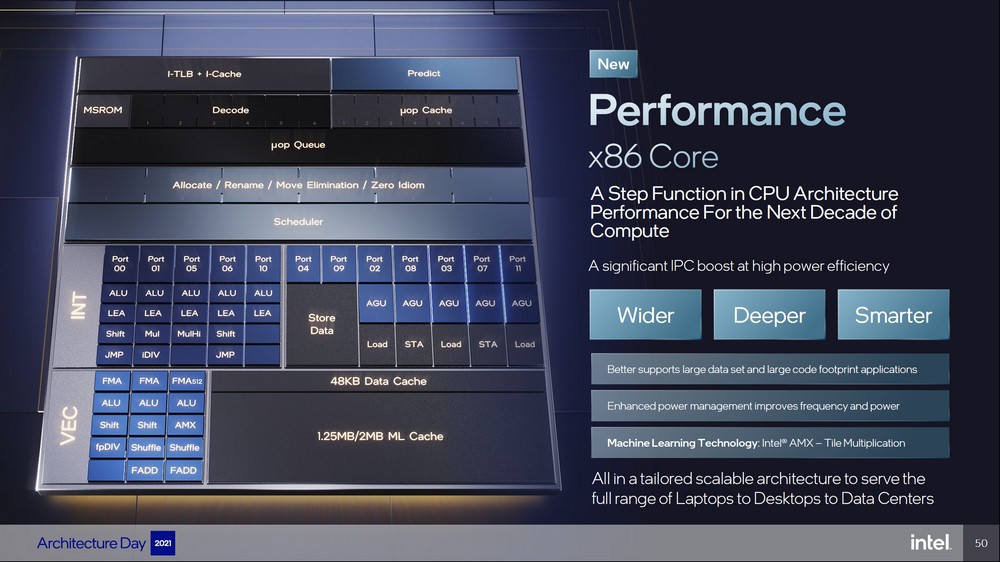

效能核心 P core

效能核心架構先前代號稱為「Golden Cove」,專注核心速度、降低延遲推向極限、單執行緒應用程式效能所設計。當工作負載的程式碼數量正不斷增長,並且要求更多的執行能力。資料也同步大幅度地成長,隨之而來的是資料頻寬需求。

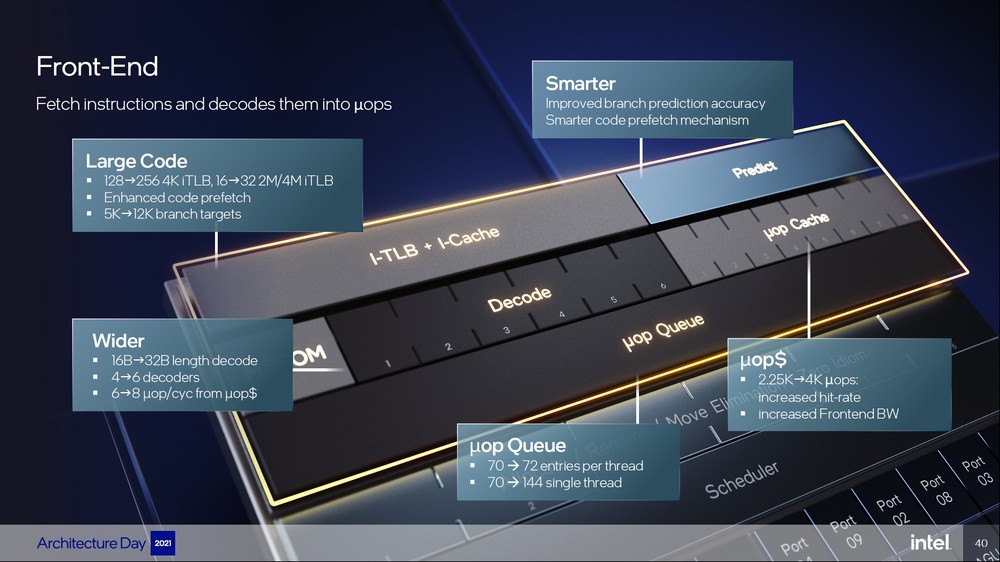

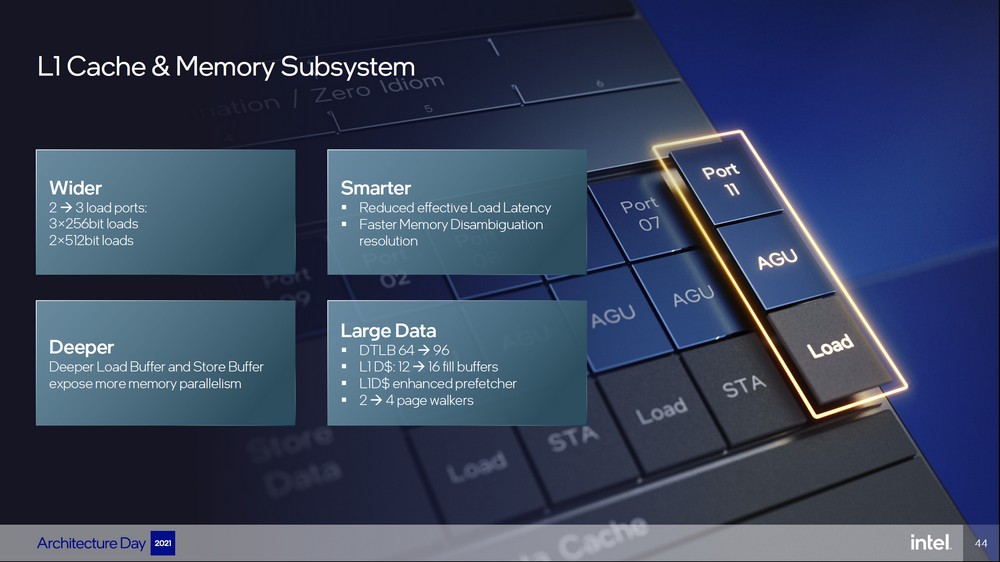

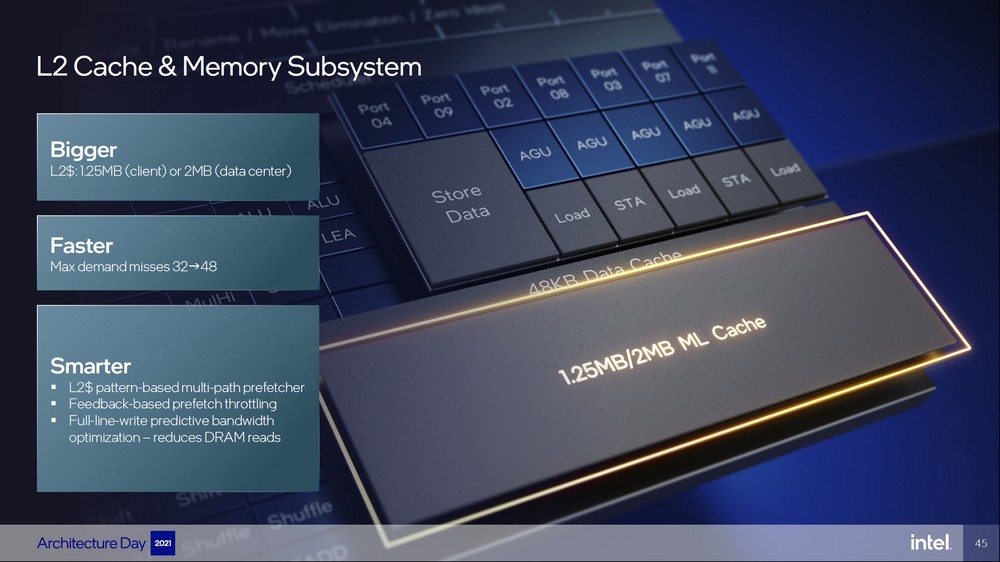

核心前端大幅度的加寬、加深,解碼器從原本的 4 個提升至 6 個、Decode Length 也從 16B 提升到 32B、微指令每週期也從 6 升級至 8 uop/cyc;而 iTLB 也從原本 128 升級至 256 4K iTLB,以及 32 2M/4M iTLB,並讓預測更有智慧,改善分支預測精準度;降低有效 L1 延遲;L2 全快取寫入預測及頻寬最佳化。

Out of Order Engine 也加寬至 6 wide allocation、12 execution port,以及更深的 512-entry Reorder 緩衝與更大的 Scheduler 容量,並可讓更多的指令於 rename / allocation 階段執行。

整數單元則有著 5 port ALU Added;Vector 執行單元則有更快的 FADD,而 FMA 支援 FP16 資料格式並加入 AVX512 支援;隨著前端、運算單元的加寬、加深,L1 與 L2 快取都跟著升級。

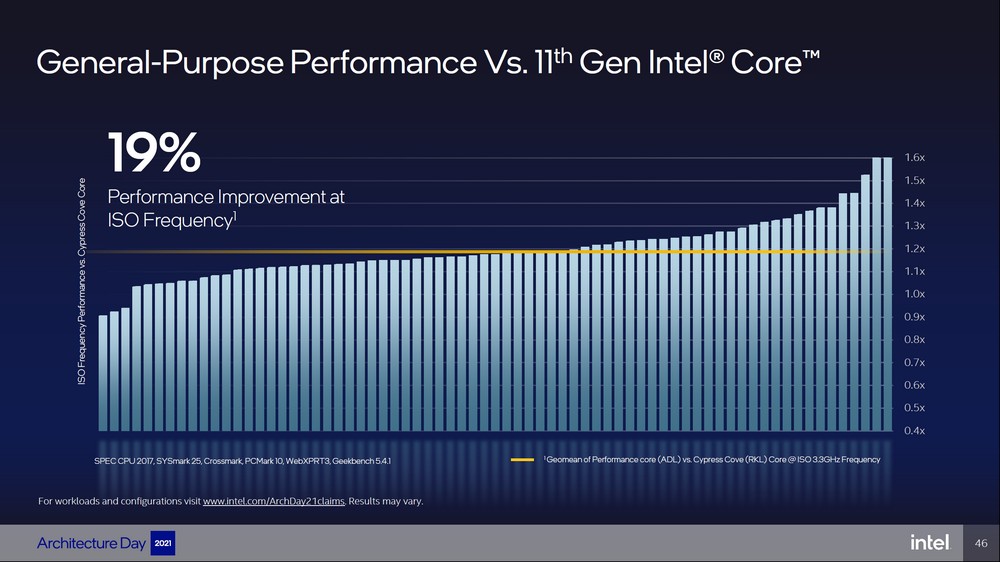

全新的效能核心 Golden Cove,於相同運作頻率之下,相較目前的第 11 代 Intel Core 架構(Cypress Cove),在廣泛及多樣的工作負載能夠提供幾何平均約 19% 的效能提升;而新的架構也具備 Intel Advanced Matrix Extensions,針對下一世代深度學習和訓練效能,而發展的內建 AI 加速。

Intel Thread Director 硬體排程單元

由於 Alder Lake 採用 P Core 與 E Core 兩種核心,CPU 除了要更有效的分配工作負載外,連同系統也要能提供最佳化的排程決策,因此在硬體當中加入 Thread Director 的改良版排程器。

通過 Thread Director 可將核心的狀態、執行緒的指令混合比例回報給作業系統,通過軟體 + 硬體的整合方式,讓作業系統有更好的執行緒排程,而這功能目前於 Windows 11 作業系統獲得最佳化。

換句話說需要系統支援下,才能真正發揮出 Alder Lake 大小核心效能,並擴大延伸 PowerThrottling API,讓開發者能夠明確辨別執行緒的服務品質屬性,並將應用分級為 EcoQoS,讓排程器能夠得知適合該執行緒的電源效率(例如將執行緒排程移至效率核心)。

Alder Lake SoC 處理器

最後回到 Alder Lake 處理器,做為 Intel 下一代的處理器,第一次次整合兩種核心類型,於多種工作負載種類均可顯著提升效能。Alder Lake 採用 Intel 7 製程打造,並支援最新的記憶體和最快的 I/O。

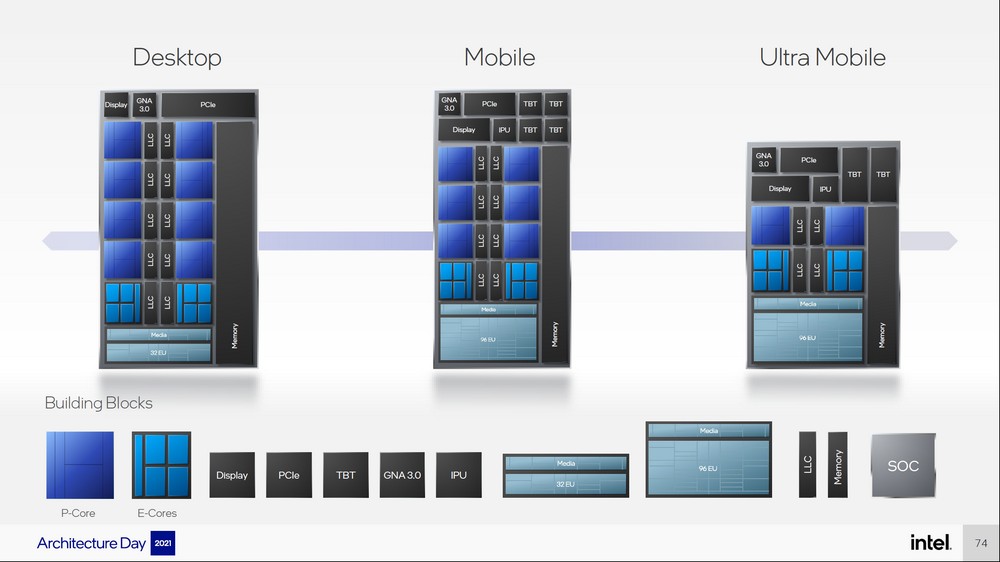

Alder Lake 將提供桌上型的 LGA 1700 腳位,以及行動平台(筆電)使用的 BGA 封裝,並有更小尺寸提供 Ultra Mobile 超薄裝置使用的版本。

Alder Lake 大量採用模組化設計,因此針對 Desktop、Mobile 與 Ultra Mobile 三種晶片規格上,主要差異在於 P-Core 與 E-Core 的數量,以及內顯、I/O 等規格。

像是目前先揭曉 Alder Lake 桌上型將具備 8 顆 P-Core 與 8 顆 E-Core,達到總共 24 執行緒、30 MB 快取的規格。

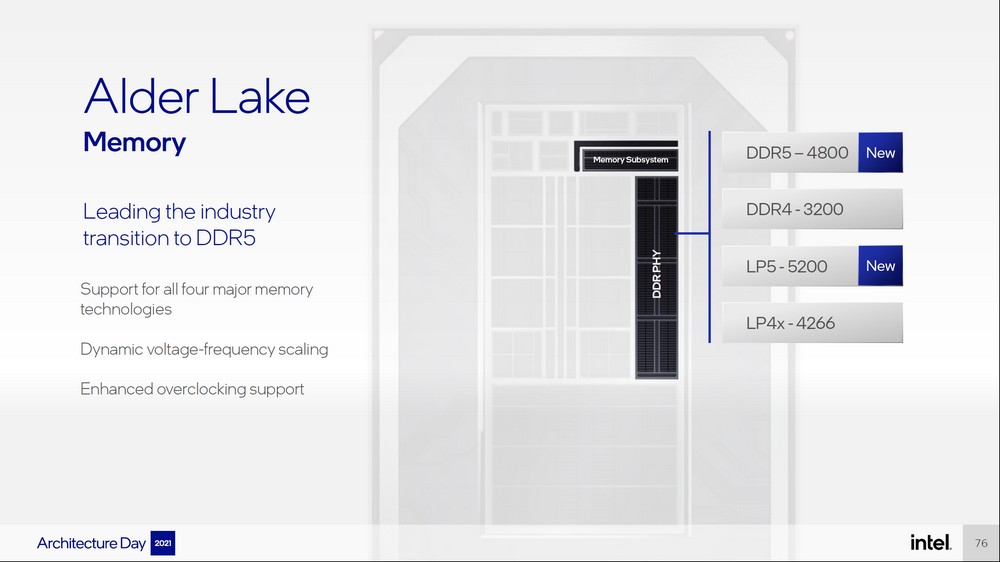

Alder Lake 除了核心架構的大更新外,也支援 DDR5-4800 記憶體規格,同時相容於 DDR4 記憶體;但根據主板廠商的規劃來看,新推出的高階平台都會以 DDR5 記憶體為主。

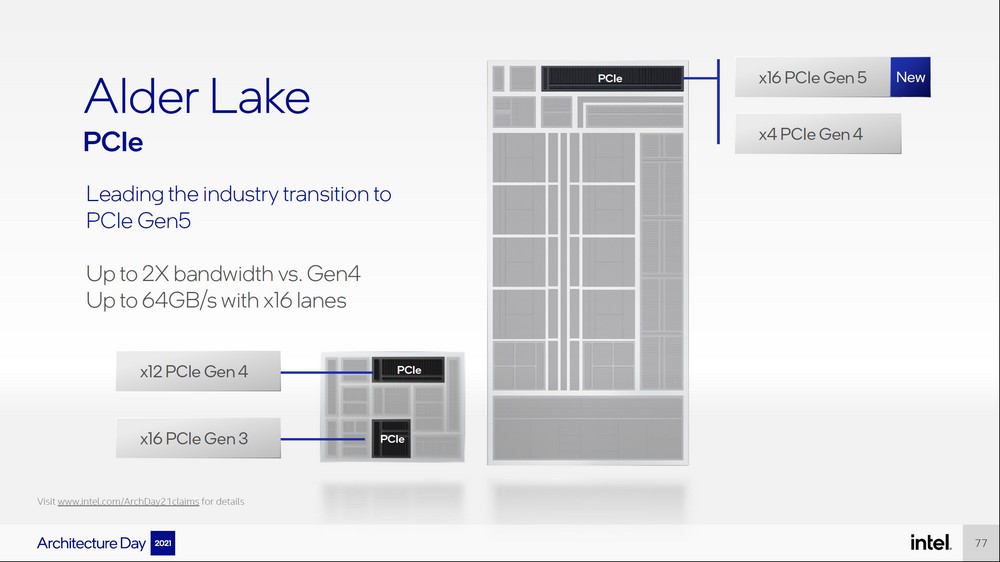

此外桌上型的 Alder Lake 也將首度支援 PCIe 5.0 x16 與 PCIe 5.0 x4 的最新規格,比起目前的 PCIe 4.0 有著翻倍的頻寬提升;只不過推出之際是否會有顯卡、SSD 支援這就要看 Intel 如何規劃了。

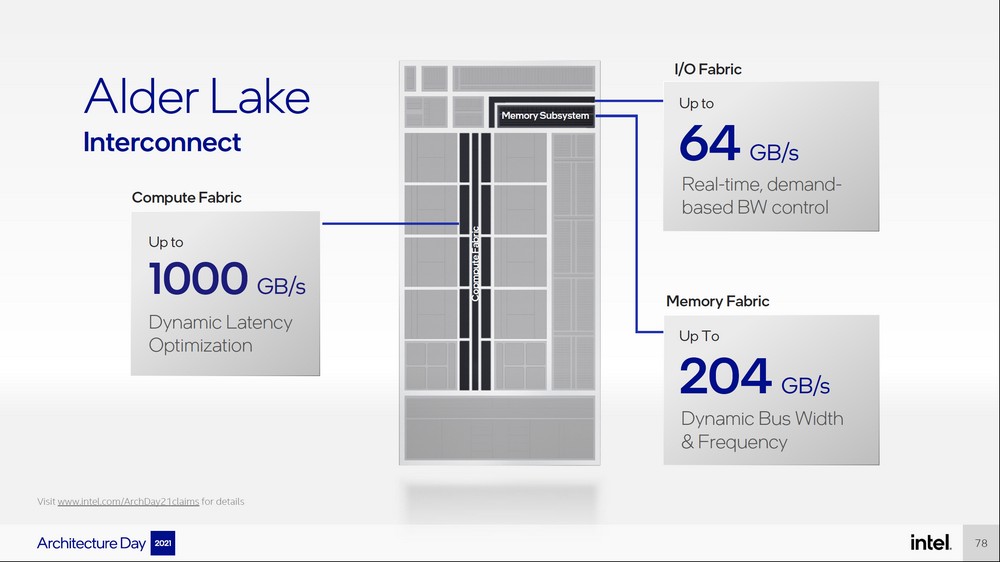

之所有 Alder Lake 可以採模組化設計,則是內部採用 Compute Fabric 連接,高達 1000 GB/s 的傳輸速度,串連著所有的 P Core 與 E Core;針對 I/O Fabric 也可達到 64 GB/s 傳輸速度,Memory Fabric 則有更高的 204 GB/s 頻寬。

從這次 Intel 架構日誠意十足的釋出滿滿的資料,看起來下一代 Alder Lake 將會是相當有趣的平台,同時也是首次 x86 核心具備大小核:P Core 與 E Core 的設計,更推進 DDR5、PCIe 5.0 等新技術。

Alder Lake 沒意外應該會在 10 月左右有更新的消息,還請各位玩家期待,Intel 這次真的很認真。