Intel宣布新的製程命名方式並加速提升達到四年五節點

Intel 公布半導體製程與封裝技術的藍圖規畫,其中半導體製程採用新的命名方法,以符合市場新的認知,並引進多項製造與多晶片封裝技術。

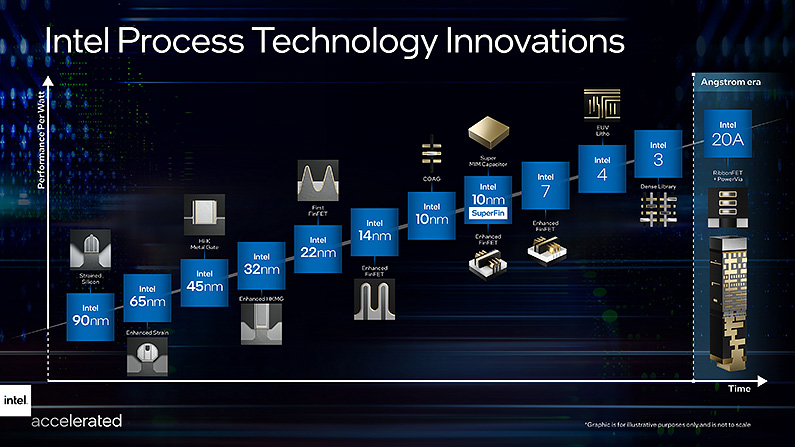

在半導體產業中領先技術多年的 Intel,目前在中央處理器市場雖然還是占有重要的地位,但是新製程一直無法順利更新,讓競爭對手有了不少可乘之機。半導體製程從過往的微米一直到現在奈米,中間經歷許多世代,而製程命名傳統上是以單一電晶體的閘極長度為基準,隨著技術的精進,不同世代的製程命名還會考慮電晶體密度等因素,但基本改變不大。

然而在 FinFET (鰭式場效電晶體)技術出現後,半導體製程命名就有差異。 FinFET 將傳統場效電晶體中三極變成更立體化,最重要是減少製程精細後更容易出現的漏電流。過去的 MOSFET 在製程變小後,閘極跟著變小而使得場效減少,再加上閘極下方氧化物變薄,汲極/源極變得靠近等因素,讓漏電流增大,這多種因素讓 FinFET 成為新選擇。但是 FinFET 的立體形式,改變了過往閘極長度的認知,這也是為何同樣 10nm 製程,Intel 和其它製造商的認知不同。雖然 Intel 近來持續解釋其製程命名方法和競爭對手的差別,但對於一般消費者或投資者而言,對手的命名更為吸引人,況且製程更新似乎也更順利。

由於現今奈米的製程節點命名方式與過往採用閘極長度為基準的傳統不同,因此 Intel 今天特別公布其製程節點的新命名方式,讓其客戶與消費者更容易認同,也與市場其它製造公司相當。隨著新製程節點的新命名,Intel 同時也宣布多項新技術,包括半導體製作、封裝等。

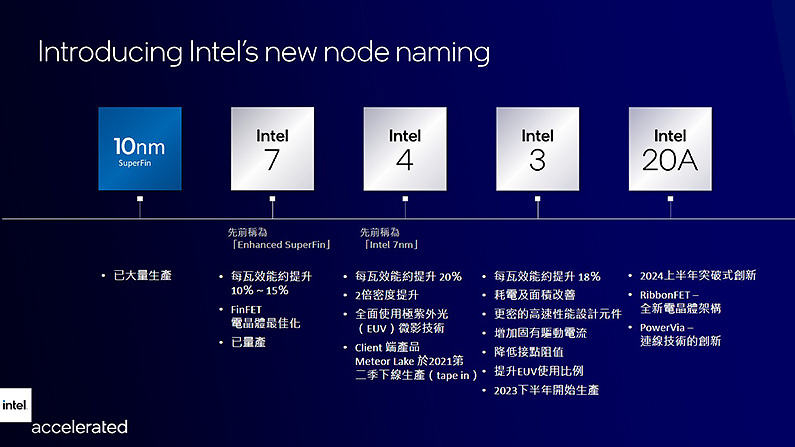

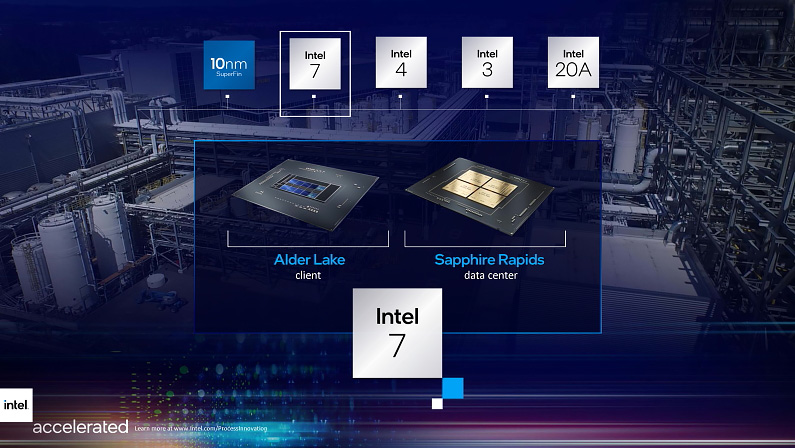

Intel 7 製程將應用在Alder Lake 以及Sapphire Rapids

新的半導體製程節點命名包括 Intel 7、Intel 4、Intel 3 與 Intel 20A等。首先是即將在今年將應用於產品的 Intel 7 製程,即過去稱為 10nm +++ Enchanced SuperFin 製程,這項製程仍是以 FinFET為基礎改良而來,透過提升應力、較低電阻材料、新的高密度曝光技術、簡化結構並使用更多金屬層擁有更佳布線等將 FinFET最佳化,預估比 10nm FinFET 每瓦效能可提升大約10%~15%。新的 Intel 7 製程將用於今年消費端的 Alder Lake 以及2022年第一季的Sapphire Rapids 資料中心產品。

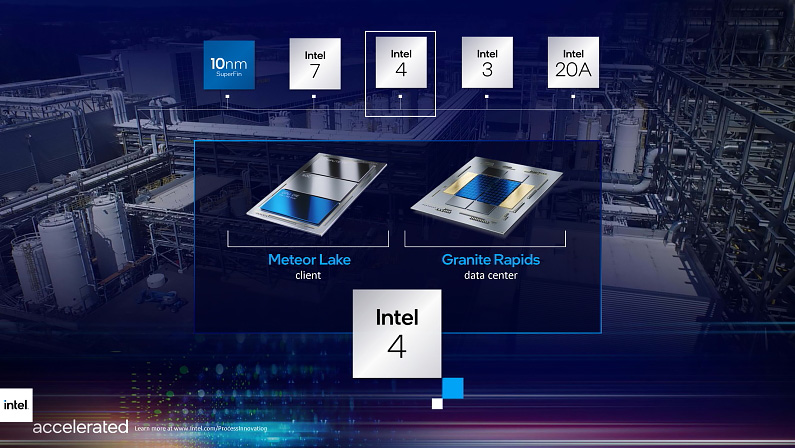

Intel 4 製程將應用在 Meteor Lake 和 Granite Rapids

過去稱為 Intel 7nm 製程這次改稱為 Intel 4,Intel 4 將是 Intel 首次全面採用極紫外光(EUV)的FinFET節點,為此將導入高度複雜的光學系統,運用波長 13.5nm 極紫外光在矽晶圓上印製極小的圖案。在此製程下預估面積有效縮小,並提升每瓦效能提升約20%。Intel 4 製程預計於 2022下半年準備量產,2023年出貨,產品將先用於消費端的 Meteor Lake 和資料中心Granite Rapids。

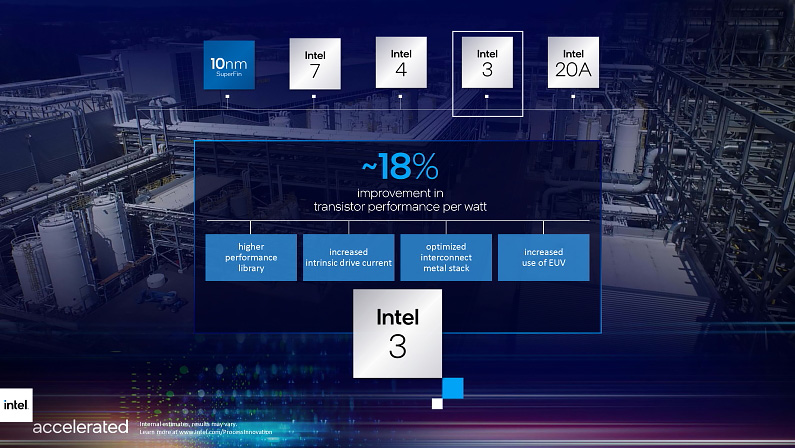

Intel 3 製程可算是 Intel 4 的改進,最主要是在於電晶體效能的改進,預密度更高、效能更高的元件庫、降低貫孔電阻的互連金屬層等。Intel 3 也會使用更高比例的EUV及更多的面積改進,預估會比 Intel 4 提入 18% 的每瓦效,預計將於2023下半年準備開始生產。

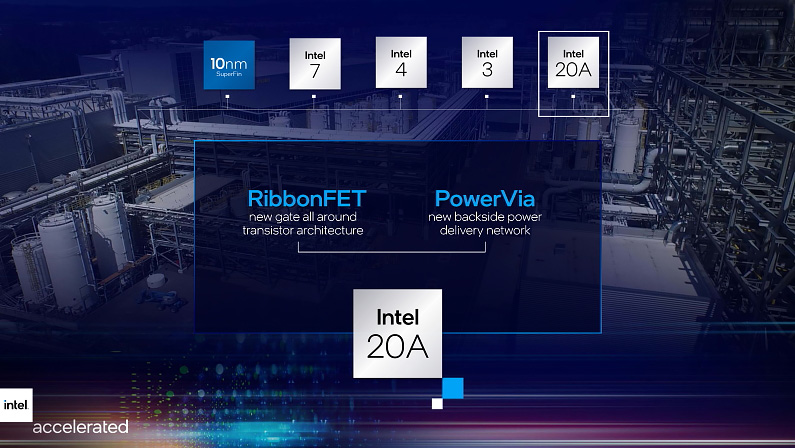

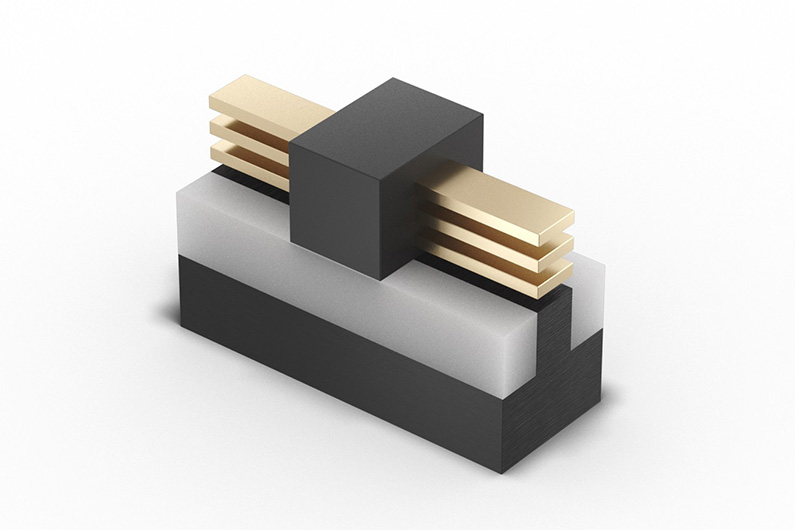

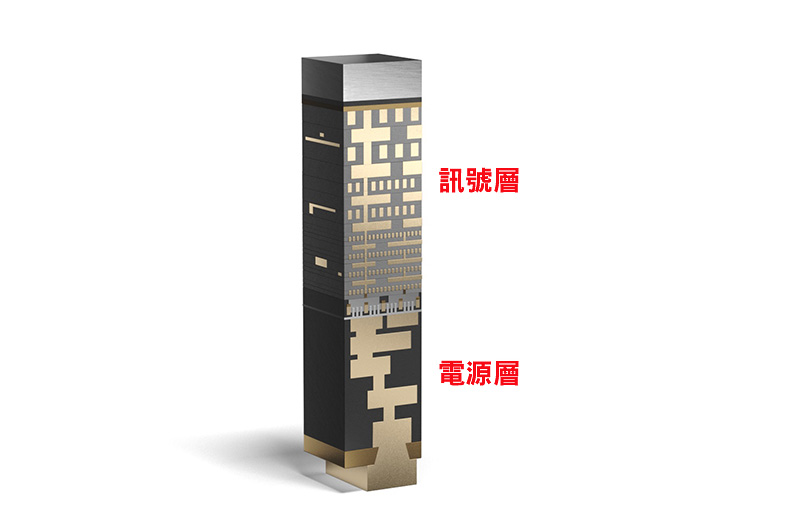

在 Intel 3製程後,Intel 預計會運用 RibbonFET和 PowerVia 等新技術推出 Intel 20A 新製程。在奈米(nm, n(nano)=10的負9次方)製程之後,就會進入更精細的世代,為了方便稱呼就改用埃米(Angstorm,Å=10的負10次方),而第一個製程就稱為 Intel 20A。此新製程採用的RibbonFET 為 Intel 環繞式閘極(Gate All Around),是 2011 FinFET 後,採全新的電晶體架構,可在較小的面積當中堆疊多個鰭片,提供提供更快的電晶體切換速度。另外還有 PowerVia 這項新技術,這是將業界首次實際運用背部供電方式,藉由將電源層集中於背部,讓訊號層可集中,以降低衰減以及減少雜訊,以達到最佳的訊號佈線。Intel 20A 預計將於 2024 年逐步量產。Intel特別宣布 Qualcomm將採用Intel 20A製程技術。

而在 Intel 20A 之後,改良自 RibbonFET 的 Intel 18A 也已進入開發階段,預計於2025年初問世,將為電晶體帶來另一次的重大性能提升。Intel同時也正在定義、建立與佈署下一世代的 EUV 工具,稱之為高數值孔徑(High-NA EUV),目前正與 ASML 緊密合作,希望能夠成功超越當代EUV。

除了新的製程之外,未來晶片的封裝技術也變得越來越重重。傳統上不同用途的晶片可能因為採用不同製程而需要個別封裝與使用,但是新一代的產品功能更多,也更需要整合在同一封裝中,需要新世代的封裝技術,因此 Intel 推宣布推出多種封裝技術。

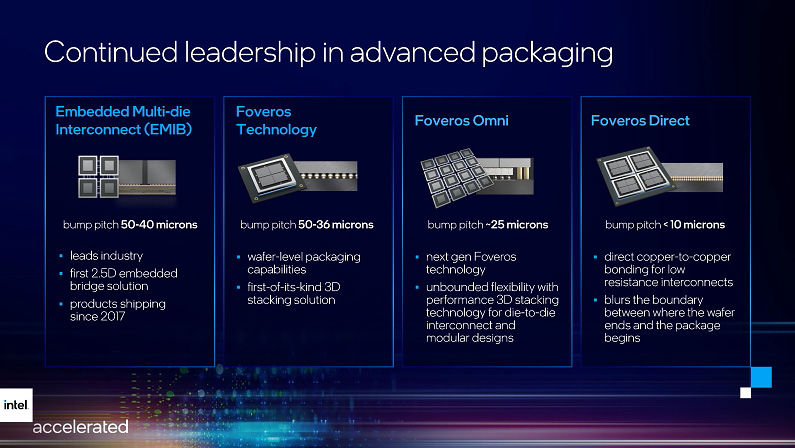

Intel 之前推出 EMIB 這款 2.5D 嵌入式橋接解決方案,擁有四片晶片並以資料中心為主的 Xeon(Sapphire Rapids)將是首款量產產品。下一世代的 EMIB 的凸點間距將從55微米降至45微米。

在晶圓級封裝方面則有 Foveris 首款3D堆疊解決方案,,其中 Meteor Lake 將是 Foveros 在消費端產品的第二世代,其凸點間距為36微米,可整合橫跨多種製程節點場晶片。

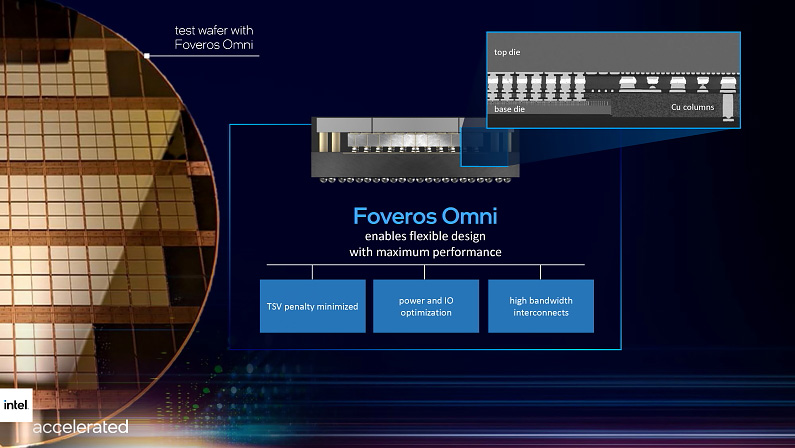

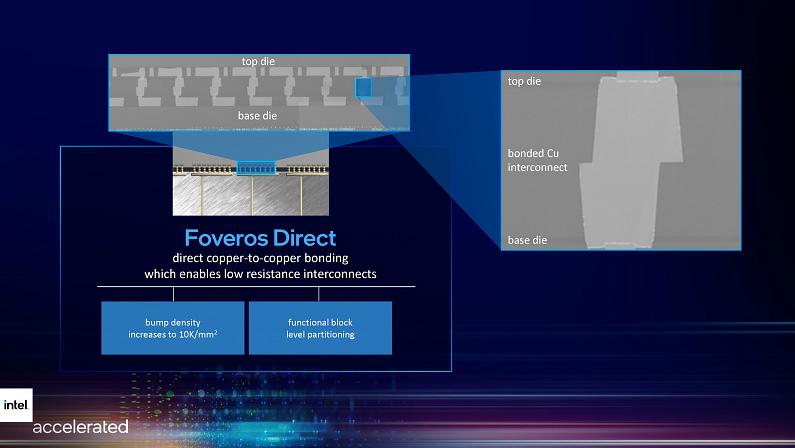

在這二項封裝技術後,Intel今日也宣布再推出 Foveros Omni和 Foveros Direct 新的封裝技術。Foveros Omni 是新一代 Foveros,其連接凸點間距將降至 25微米,採用晶片與晶片連結與模組化設計,提供靈活且高效能3D堆疊技術。Foveros Omni 允許混合多個頂層晶片與多個基底晶片,更可橫跨多種晶圓廠節點的分拆晶片(die disaggregation),預計將於2023年準備大量生產。

而 Foveros Direct 是 Foveros Omni 的補充技術,連接凸點間距將低於 10 微米,且為了降低互連阻抗,改採直接銅對銅接合技術,這也使得晶圓製造終點與封裝起點的界線變得模糊。Foveros Direct 將大幅提升3D堆疊的密度,並為封裝技術帶來新的局面,預估將於 2023年問世。