國際固態電路研討會: SK Hynix 介紹自家首款 DDR5 晶片

儘管 JEDEC 尚未完成 DDR5 最終標準的開發,但晶片大廠之間早就開始了暗自較勁。在 San Francisco 舉辦的國際固態電路研討會 ( ISSCC ) 上, SK Hynix 首次詳細介紹了自家以 DDR5 規範為基礎的同步 DRAM 晶片。作為同樣來自韓國的競爭對手,三星在同一會議上描述了以低功耗 LPDDR5 規範為基礎的 DSRAM 作為反擊。

與目前已問世的 DDR4 標準對比, DDR5 能夠提供雙倍的頻寬密度,以及更高的通道效率。原定於去年完成的 DDR5 標準,現仍在持續中,預計相關產品會在今年年底開始出現。

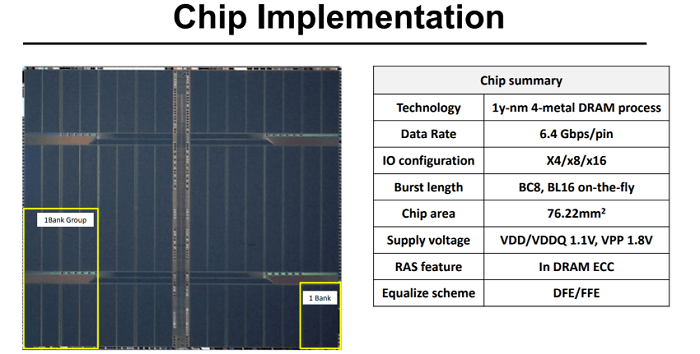

在週三的國際固態電路研討會上,海力士晶片設計師 Dongkyun Kim 發表了自家首款 DDR5 晶片的報告。

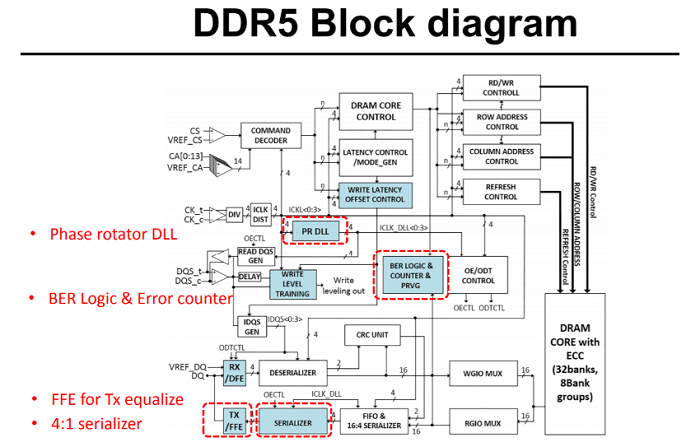

Kim 對延遲鎖定回路的部分改動進行了深入講解,表示 Hynix 借助了相位旋轉器和注入鎖定振盪器,達到了對延遲鎖定環 ( DLL ) 的修改。以減少在較高時鐘速度下,操作相關的時鐘抖動和占空比失真。

他還描述了海力士設計團隊使用的其它技術,包括用於抵消與更高速度相關的時鐘域問題的寫入等級訓練方法,以及改進的前向回饋均衡 ( FFE ) 電路。

與此同時,三星公司描述了一款 10nm 級別的 LPDDR5 SDRAM 。在低至 1.05V 的電壓下,它可以達到 7.5 Gb/s 的速率。

JEDEC 在本周早些時候發佈了 LPDDR5 標準,最終定下的標準 I/O 運行速率為 6400 MT/s ,較 LPDDR4 時代提升了 50% 。

如此一來,業界有望大幅提升智慧手機、平板電腦、以及超輕薄筆電等應用場景下的記憶體速度和效率。此外, Objective Analysis 首席分析師 Jim Handy 披露了三星 LPDDR5 新品的更多技術細節。