Intel Xe GPU架構詳細訊息– Ponte Vecchio Xe HPC Exascale GPU,擁有1000個EU,大容量HBM,Rambo快取

Intel剛剛在其HPC開發者大會上公佈了其採用Xe GPU架構的產品的最新詳細訊息。Intel高級副總裁兼架構首席架構師兼架構總經理Raja Koduri在會議上發表講話,透漏了Intel首個內部顯示架構Xe的第一個架構路線圖,以及將嵌入其中的各個產品線。

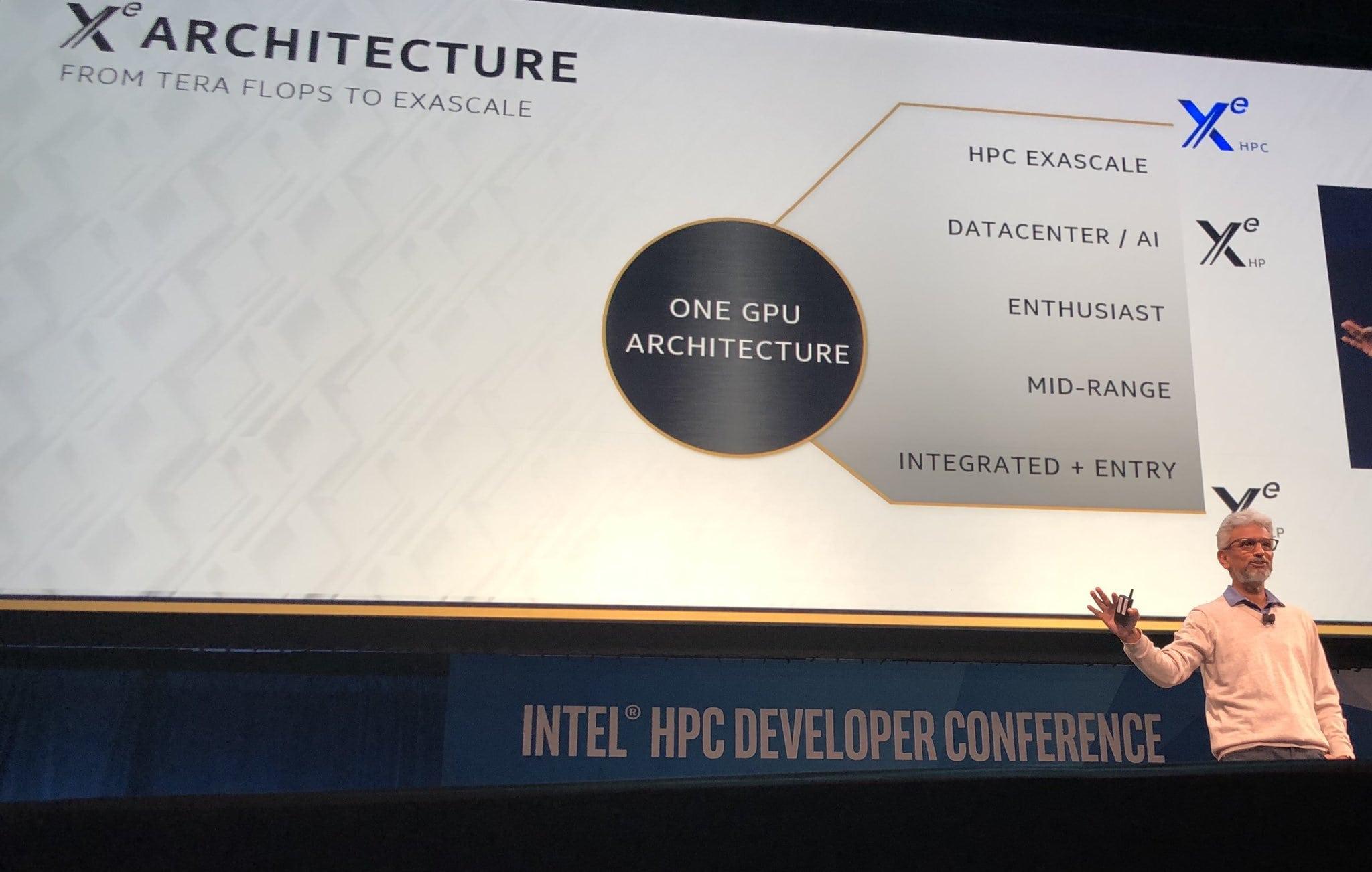

這裡有很多要討論的內容,所以讓我們談談Xe GPU架構的第一個方面,即產品本身。Intel Xe GPU架構採用可提供為各種產品的一種可擴充架構。Intel計劃提供三種來自Xe的架構設計。這些包括:

Intel Xe LP(整合+入門)

Intel Xe HP(中階,發燒友,數據中心/人工智慧)

Intel Xe HPC(HPC Exascale)

從命名方案中您就可以知道這些GPU的功能。“ LP”關鍵字代表“低功耗”,而“ HP”關鍵字代表“高性能”。HPC關鍵字只是針對高性能計算的架構,它將使用我們將要討論的一系列新的Intel技術。據說Xe LP約為5W-20W,但最多可到50W。Intel的Xe HP高出一節,覆蓋75W-250W的市場,而Xe HPC架構應該更高,從而提供比其他產品更高的計算性能。

Raja特別談到了Xe HPC GPU,因為這是開發者大會的全部內容。Intel的Xe HPC GPU可以擴充到1000個EU,並且每個執行單元都進行了升級,以提供比40倍更多的雙精度浮點計算能力。EU也將稱為XEMF(XE Memory Fabric的簡稱)的新可擴充記憶體架構連接到多個高頻寬記憶體通道。Xe HPC架構還將包括一個稱為Rambo快取的超大型統一快取,它將多個GPU連接在一起。通過提供巨大的記憶體頻寬,該Rambo快取將在整個雙精度工作負載中提供可持續的峰值FP64計算性能。

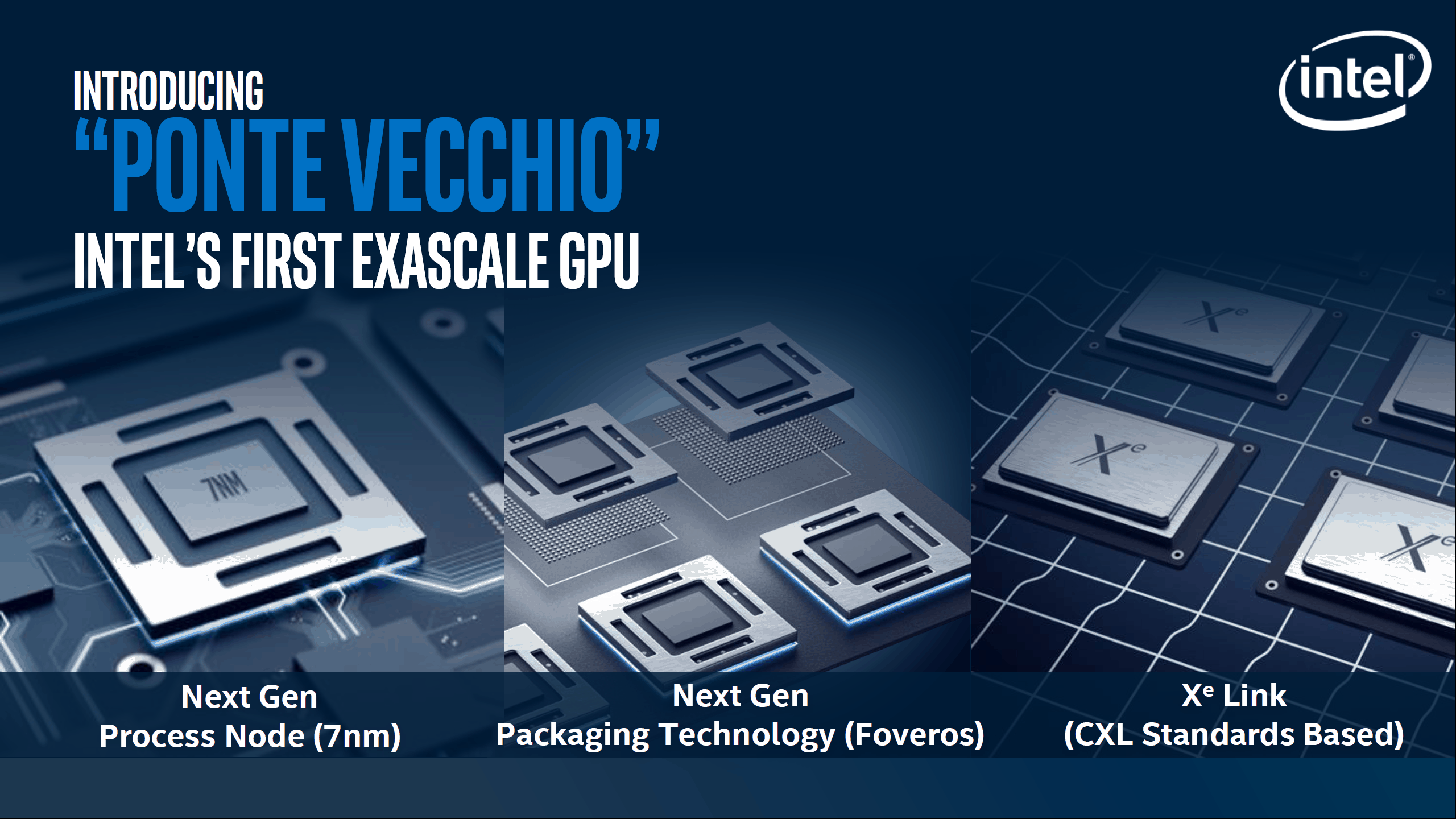

XE Memory Fabric將在最新的7nm製程上打造其Xe HPC GPU。這也是Intel先前談到的7nm產品。Intel將充分利用其新的和增強的封裝技術(例如Forveros和EMIB互連)來開發下一代百億億次GPU。就製程優化而言,以下是Intel宣布的針對其10nm以上7nm製程的一些關鍵改進:

Xe HPC GPU將使用Forveros技術與Rambo快取互連,而Rambo快取將在同一中介層上在其他多個Xe HPC GPU之間共享。同樣EMIB將用於將HBM與GPU連接。兩種技術都將帶來頻寬效率和密度的巨大飛躍。就像他們的Xeon兄弟一樣,Intel的Xe HPC GPU將配備ECC記憶體/快取校正和Xeon-Class RAS。

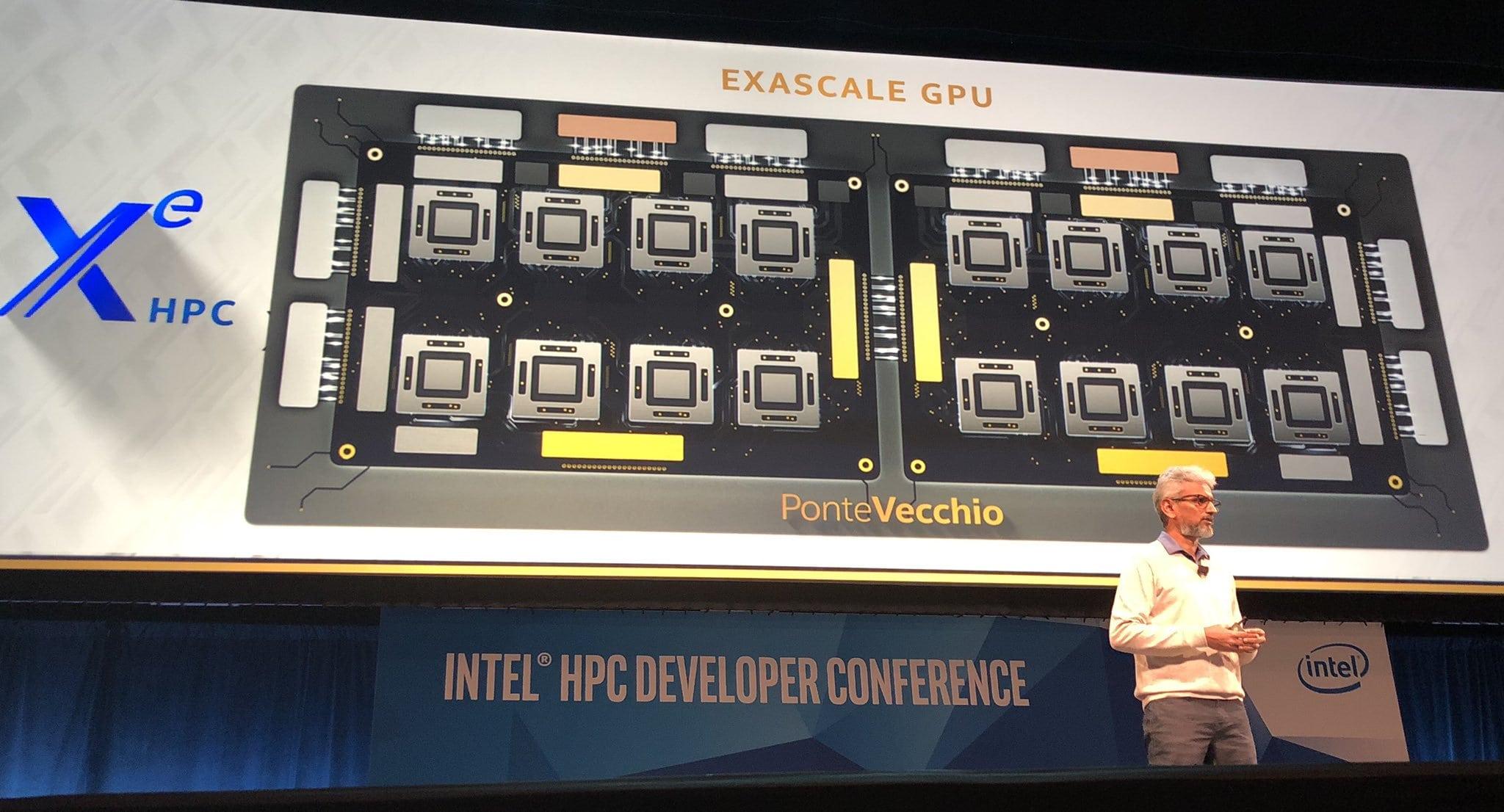

詳細介紹了所有關鍵技術之後,我們直接介紹將採用Intel Xe HPC架構的首款7nm產品。它稱為Ponte Vecchio,一種超大規模GPU,旨在成為超級計算機的下一個單晶片百億億級設計。Ponte Vecchio GPU將配備16個採用Xe HPC GPU架構的計算小晶片。

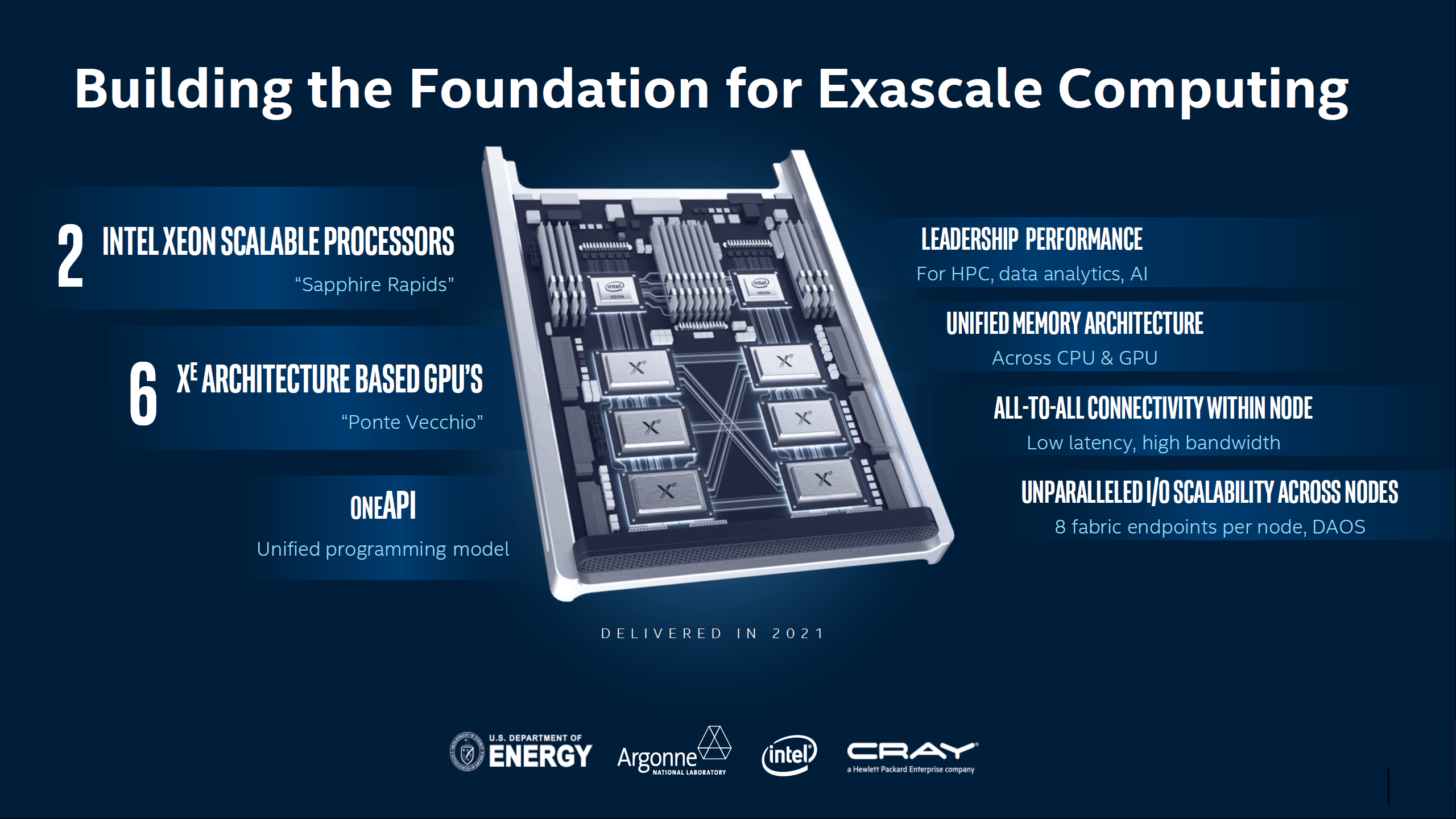

每個GPU似乎都連接有大量的HBM DRAM。這裡還詳細介紹了Aurora超級電腦的單個節點。正在研究通過Intel使用CXL(Compute Express Link或Intel Xe Link)和OneAPI軟體堆棧透過Intel連接的六個Ponte Vecchio GPU 。該節點還將配備2個採用下一代10nm++ Willow Cove CPU架構的Intel Sapphire Rapids處理器。如上所述首款採用採用Xe的7nm數據中心Ponte Vecchio PGPU的確認產品將是Aurora超級電腦。

這種方法與NVIDIA使用NVIDIA DGX-2的方式非常相似,將16個Volta GPU堆疊在單個節點中,然後通過NVSwitch連接它們。但是與Intel的計劃不同的是,NVIDIA將整個節點稱為GPU,而Intel則將單個插入器中的16個小晶片稱為GPU。在單個節點上有六個這樣的GPU。NVIDIA可能還會在其未來的HPC產品(例如Ampere)上採用MCM(多晶片模組模塊)芯片設計,該產品有望在2020年(Intel的Ponte Vecchio進入HPC市場的前一年)首次亮相。

雖然Datacenter將首先使用7nm Xe GPU,但Intel的10nm Xe GPU產品將在2020年進入主流和發燒級遊戲市場。