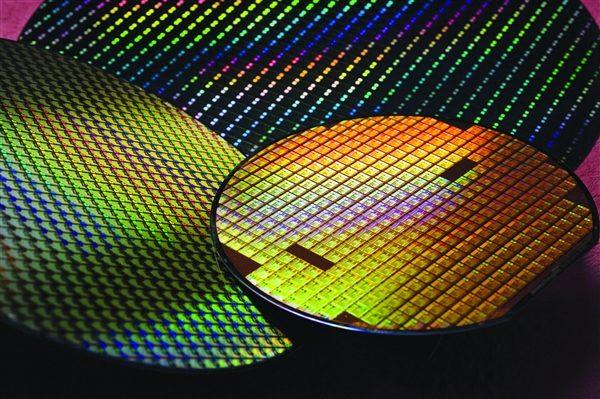

TSMC 5nm 測試晶片良率已達80%:明年上半年大規模量產

IEEE IEDM大會上,台積電官方披露了5nm工藝的最新進展,給出了大量確鑿數據,看起來十分的歡欣鼓舞。

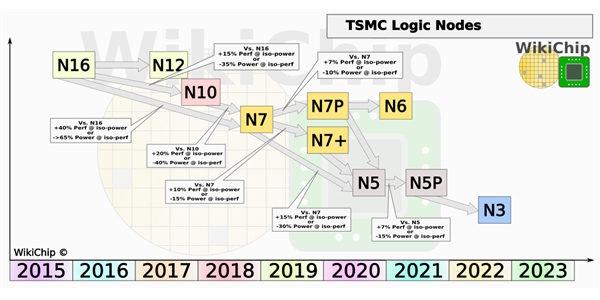

5nm將是台積電的又一個重要工藝節點,分為N5、N5P兩個版本,前者相比於N7 7nm工藝性能提升15%、功耗降低30%,後者在前者基礎上繼續性能提升7%、功耗降低15%。

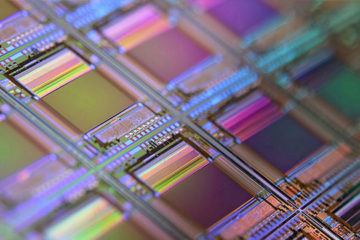

台積電5nm將使用第五代FinFET晶體管技術,EUV極紫外光刻技術也擴展到10多個光刻層,整體晶體管密度提升84%——7nm是每平方毫米9627萬個晶體管,5nm就將是每平方毫米1.771億個晶體管。

台積電稱5nm工藝目前正處於風險試產階段,測試晶片的良品率平均已達80%,最高可超過90%,不過這些晶片都相對很簡單,如果放在復雜的移動和桌面芯片上,良品率還做不到這麼高,但具體數據未公開。

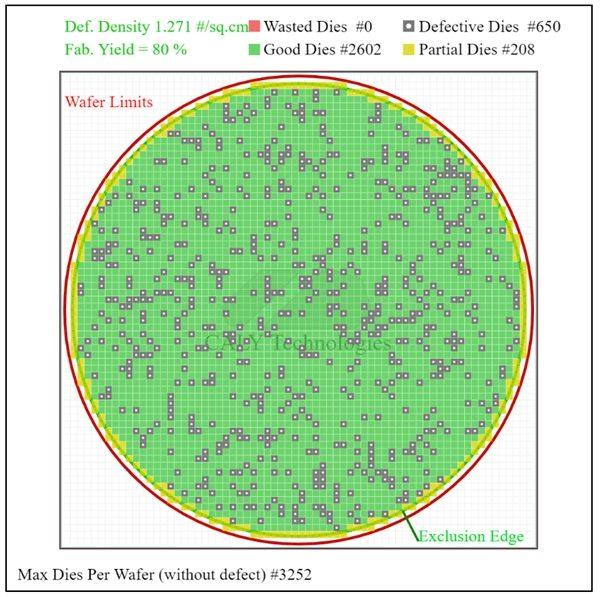

具體來說,台積電5nm工藝的測試晶片有兩種,一是256Mb SRAM,單元面積包括25000平方納米的高電流版本、21000平方納米的高密度版本,後者號稱是迄今最小的,總面積5.376平方毫米。

二是綜合了SRAM、CPU/GPU邏輯單元、IO單元的,面積佔比分別為30%、60%、10%,總面積估計大約17.92平方毫米。

按照這個面積計算,一塊300mm晶圓應該能生產出3252顆晶片,良品率80%,那麼完好的晶片至少是2602個,缺陷率1.271個每平方厘米。

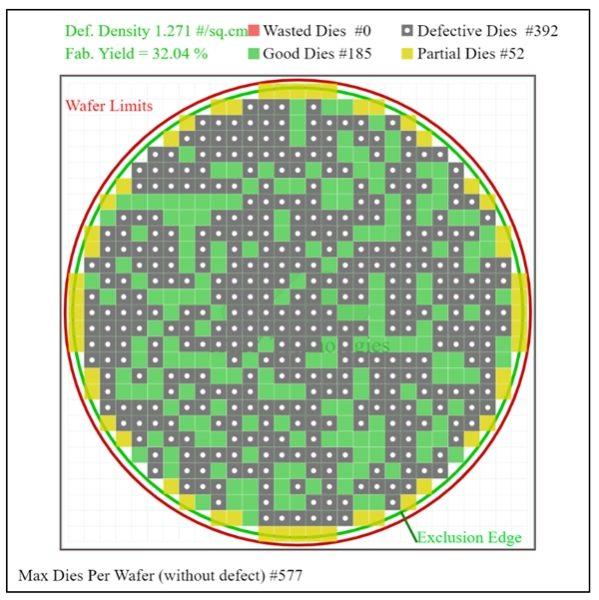

當然,現代高性能晶片面積都相當大,比如麒麟990 5G達到了113.31平方毫米。

按照一顆晶片100平方毫米計算,1.271個每平方厘米的缺陷意味著良品率為32%,看著不高但對於風險試產階段的工藝來說還是完全合格的,足夠合作夥伴進行早期測試與評估。

另外,AMD Zen2架構每顆晶片(八核心)的面積約為10.35×7.37=76.28平方毫米,對應良品率就是41%。

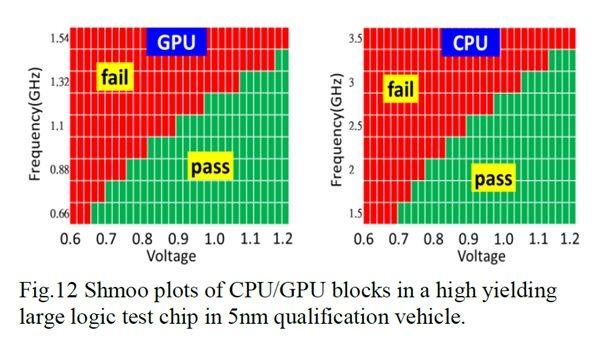

台積電還公佈了5nm工藝下CPU、GPU晶片的電壓、頻率對應關係,CPU通過測試的最低值是0.7V、1.5GHz,最高可以做到1.2V 3.25GHz,GPU則是最低0.65V 0.66GHz、最高1.2V 1.43GHz。當然這都是初步結果,後續肯定還會大大提升。

台積電預計,5nm工藝將在2020年上半年投入大規模量產,相關晶片產品將在2020年晚些時候陸續登場,蘋果A14、華為麒麟1000系列、AMD Zen4架構四代銳龍都是妥妥的了,只是據說初期產能會被蘋果和華為基本吃光。