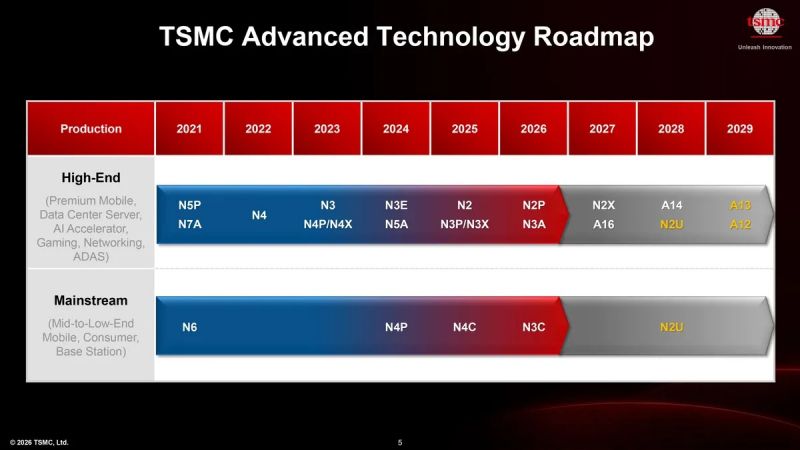

台積電公佈A12/A13工藝, 2nm製程節點也將擴展出N2U

近日,台積電(TSMC)舉辦了“2026年北美技術研討會”,更新了至2029年的工藝技術路線圖,首次公佈了A14製程節點衍生的A13和A12工藝,另外還宣布擴展2nm製程節點,帶來了N2U工藝。

TomsHardware報道,A13是A14的漸進式改進,主要透過光學收縮實現將面積減小了約6%,變得更加緊湊高效,同時保持完整的設計規則和電氣兼容性,使客戶透過最小的設計改動即可受益,預計2029年進入量產階段,下一代以滿足人工智慧(AI)、高效能運算(HPC)和行動運算客戶需求。 A13延續了台積電過去的做法,提供了原製程節點上最佳化改進的工藝,包括N12、N6、N4和N3P都是類似的想法。

台積電也預覽了A12,這是A14的增強型產品,支援超級電軌(Super Power Rail)架構,也就是背面供電技術,也計畫在2029年量產。同時,台積電也在2nm製程節點上擴展出了N2U,透過設計與技術協同優化,相同功率下帶來了3%至4%的性能提升,或者相同速度下功耗下降8%至10%,同時邏輯密度踢死了2%至3%,屬於利用成熟技術的平衡選擇,計劃2028年量產。

過去很長一段時間,台積電主要收入支柱是智慧型手機產業,不過隨著過去幾年AI和HPC興起,已經超越了行動晶片成為第一大收入來源。為此台積電在最新的路線圖上有意加入了分化的策略,依終端需求細分前緣節點,而非一刀切的方案。一方面提供N2、N2P、N2U、A14和A13面向智慧型手機和客戶端設備,這部分需求看重成本、能源效率和IP復用,且強調設計相容性,適合漸進式改進,可以每年更新一次。另一方面,N2X、A16和A12面向AI和HPC應用,這部分需求屬於不惜一切代價追求最大性能,提供切實可及的性能、功耗和晶體管密度提升,而且不那麼在意成本,計劃每兩年升級一次。

值得注意的是,台積電現已將A16放置在2027年,而不是之前的2026年,理論上是延誤了。

除了常規的製程技術外,台積電還計劃在2028年帶來首個採用GAA電晶體架構的車用級製程技術N2A。與今年量產的N3A相比,N2A在相同功率下帶來了15%至20%的速度提升,計劃於2028年完成AEC-Q100認證。台積電還在N2P製程設計套件中提供了「Auto-Use」設計套件,使客戶能夠在設計中考慮汽車使用條件,以便更早開始設計工作。

台積電今年也打算將高壓技術引入FinFET電晶體架構,帶來以DDIC為導向的N16HV製程。相較於過去的N28HV,N16HV的閘極密度提高了41%,功耗則降低了35%。對於近眼顯示(Near-Eye Display, NED)設備來說,N16HV可以將晶片面積減少40%,功率降低超過20%。

另外截至2029年,台積電還沒有任何涉及使用High-NA EUV光刻機的技術,即便是路線圖上最先進的A13和A12。相較之下,英特爾在Intel 14A及其之後的製程節點上都打算加入High-NA EUV光刻機,也就是2027年至2028年左右啟用,與台積電的做法形成了鮮明的對比。